本文为明德扬原创及录用文章,转载请注明出处!

1.1 总体设计

1.1.1 概述

LED数码管以发光二极管作为发光单元,颜色有单红,黄,蓝,绿,白,黄绿等效果,并且可以构造成“8”字形。数码管根据LED的接法不同分为共阴和共阳两类,它们的发光原理是一样的,只是它们的电源极性不同而已。

数码管可以通过驱动电路来驱动内部的各个段码,从而显示出需要的数字。根据数码管驱动方式的不同,可以将其分为静态式和动态式两类。

1.1.2 设计目标

完成数码管的显示,具体功能要求如下:

1. 间隔1s切换数码管位选,做到数码管从左到右流动显示的效果;

2. 数码管显示的数值从0开始,每切换一位位选数值加一;

1.1.3信号列表

1.1.4设计思路

- 数码管显示原理

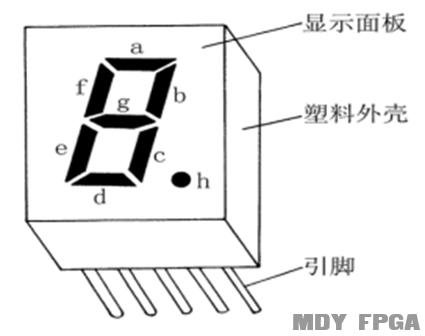

数码管的8个显示字段”a、b、c、d、e、f、g、h”对应显示面板的位置如下图所示。

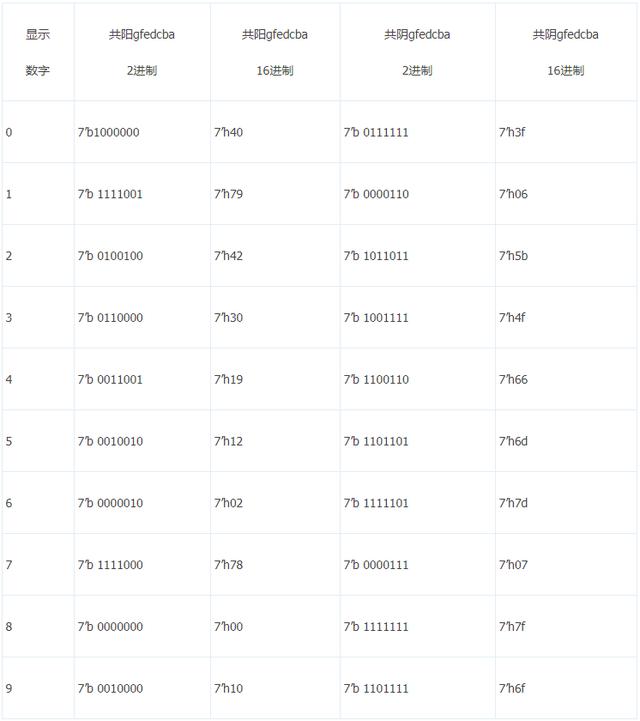

数码管显示数字0到9对应的gfedcba值如下表所示。

表5- 1 数码管显示数字与字段值的对应关系

数码管静态驱动是指每个数码管的每一个段码都通过一个I/O端口进行驱动,或使用如BCD码二-十进制译码器译码进行驱动,也称直流驱动。静态驱动编程简单,显示亮度高,但占用的I/O端口多,这里不使用这种方法。

数码管动态驱动是将所有数码管的8个显示字段"a、b、c、d、e、f、g、h"的同名端连接在一起,此外每个数码管的公共极COM需增加由各自独立I/O线控制的位选通控制电路。当要输出某一字形码时,所有数码管都会接收到相同的字形码,但究竟是哪个数码管会显示出字形取决于单片机对位选通COM端电路的控制。只需将显示数码管的选通控制打开,该位就会显示出字形,而没有选通的数码管并不会点亮。数码管特定的发光二极管段加上电压后,这些特定的段就会发亮,并且当每位元数码管的点亮时间为1~20ms,由于人的视觉暂留现象及发光二极体的余辉效应,尽管实际上各位数码管并非同时点亮,但只要扫描的速度足够快,给人的印象就是一组稳定的显示资料,不会有闪烁感,使得动态显示的效果和静态显示是一样的,这样能够节省大量的I/O口,而且功耗更低。

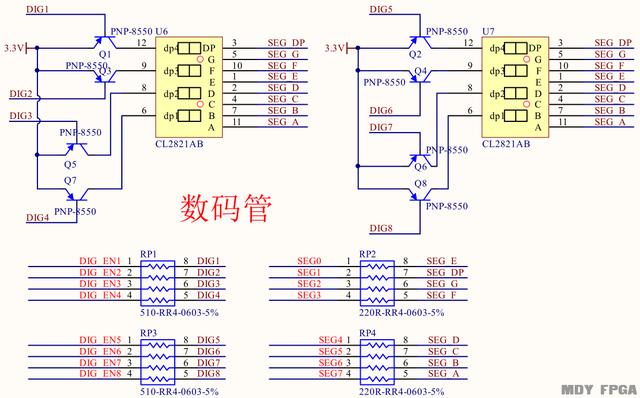

以下是MP801开发板对应的数码管原理图,并且是共阳极的数码管:

- 工程架构

根据设计目标将现象翻译成信号表示如下:

第1秒,数码管0显示数字“0”,即seg_sel的值为8’b1111_1110,seg_ment的值为8’b1100_0000;

第2秒,数码管1显示数字“1”,即seg_sel的值为8’b1111_1101,seg_ment的值为8'b1111_1001;

第3秒,数码管2显示数字“2”,即seg_sel的值为8’b1111_1011,seg_ment的值为8'b1010_0100;

第4秒,数码管3显示数字“3”,即seg_sel的值为8’b1111_0111,seg_ment的值为8'b1011_0000;

第5秒,数码管4显示数字“4”,即seg_sel的值为8’b1110_1111,seg_ment的值为8'b1001_1001;

第6秒,数码管5显示数字“5”,即seg_sel的值为8’b1101_1111,seg_ment的值为8'b1001_0010;

第7秒,数码管6显示数字“6”,即seg_sel的值为8’b1011_1111,seg_ment的值为8'b1000_0010;

第8秒,数码管7显示数字“7”,即seg_sel的值为8’b0111_1111,seg_ment的值为8'b1111_1000;

第九秒,回到数码管0显示数字“0”,以此进行循环。

总结发现,数码管每隔1秒进行变化,且8个数码管轮流显示。

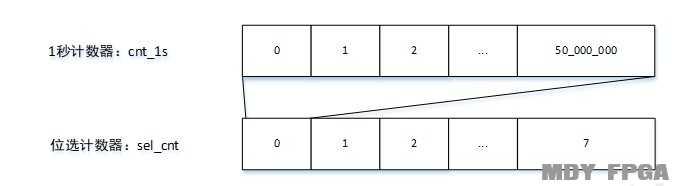

因此本工程用到了三个计数器的架构,具体架构如下图所示:

1秒计数器cnt_1s:用于计算1s的时间,加一条件为1,表示一直在计数;数到50,000,000下,表示数到1s就结束。

位选计数器sel_cnt:用于区分选通的数码管,加一条件为end_cnt_1s,表示每间隔1秒的时间后,切换选通下一个数码管;数到8下,表示8个数码管都选通过一轮了。

1.1.5参考代码

module seg_disp(

rst_n ,

clk ,

seg_sel ,

segment

);

parameter TIME_1S = 50_000_000 ;

parameter SEG_WID = 8 ;

parameter SEG_NUM = 8 ;

parameter CNT_WID = 10 ;

parameter TIME_20US = 10'd1000 ;

parameter NUM_0 = 8'b1100_0000;

parameter NUM_1 = 8'b1111_1001;

parameter NUM_2 = 8'b1010_0100;

parameter NUM_3 = 8'b1011_0000;

parameter NUM_4 = 8'b1001_1001;

parameter NUM_5 = 8'b1001_0010;

parameter NUM_6 = 8'b1000_0010;

parameter NUM_7 = 8'b1111_1000;

parameter NUM_8 = 8'b1000_0000;

parameter NUM_9 = 8'b1001_0000;

parameter NUM_ERR = 8'b1111_1111;

input clk ;

input rst_n ;

output [SEG_WID - 1:0] seg_sel ;

output [SEG_WID - 1:0] segment ;

reg [SEG_WID - 1:0] seg_sel ;

reg [SEG_WID - 1:0] segment ;

reg [ 31 : 0] cnt_1s ;

reg [SEG_NUM - 1:0] sel_cnt ;

reg [ 4 - 1 : 0] seg_tmp ;

wire add_cnt_1s ;

wire end_cnt_1s ;

wire add_sel_cnt ;

wire end_sel_cnt ;

always @(posedge clk or negedge rst_n) begin

if (rst_n==0) begin

cnt_1s <= 0;

end

else if(add_cnt_1s) begin

if(end_cnt_1s)

cnt_1s <= 0;

else

cnt_1s <= cnt_1s+1 ;

end

end

assign add_cnt_1s = 1;

assign end_cnt_1s = add_cnt_1s && cnt_1s == TIME_1S-1 ;

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

sel_cnt <= 0;

end

else if(add_sel_cnt)begin

if(end_sel_cnt)

sel_cnt <= 0;

else

sel_cnt <= sel_cnt + 1;

end

end

assign add_sel_cnt = end_cnt_1s;

assign end_sel_cnt = add_sel_cnt && sel_cnt == SEG_NUM-1;

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

seg_sel <= {SEG_NUM{1'b1}};

end

else begin

seg_sel <= ~(1'b1 << sel_cnt);

end

end

always @(*)begin

if(rst_n==1'b0)

seg_tmp = {SEG_NUM{1'b1}};

else

seg_tmp = sel_cnt ;

end

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

segment<=NUM_0;

end

else begin

case (seg_tmp)

0 : segment <= NUM_0;

1 : segment <= NUM_1;

2 : segment <= NUM_2;

3 : segment <= NUM_3;

4 : segment <= NUM_4;

5 : segment <= NUM_5;

6 : segment <= NUM_6;

7 : segment <= NUM_7;

8 : segment <= NUM_8;

9 : segment <= NUM_9;

default : segment <= NUM_ERR;

endcase

end

end

endmodule

1.2 效果和总结

-

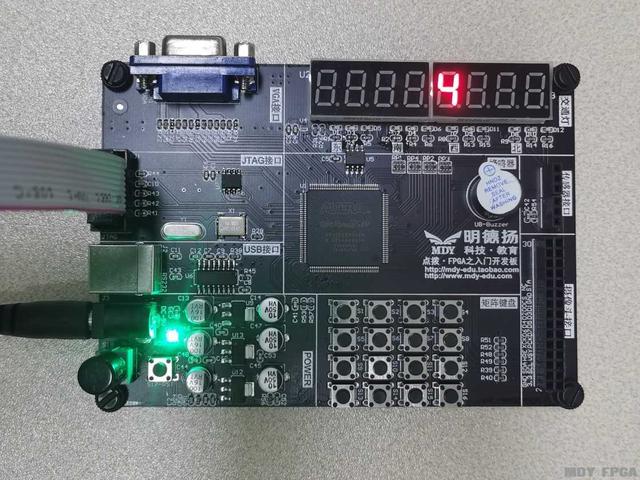

下图是该工程在db603开发板上的现象

-

下图是该工程在mp801开发板上的现象

-

下图是该工程在ms980试验箱上的现象

由于该项目的上板现象是上电数码管从左到右流动显示对应的数值,想观看完整现象的朋友可以看一下现象演示的视频。

设计教学视频及工程源代码请移步明德扬论坛学习。

感兴趣的朋友也可以访问明德扬论坛(www.FPGAbbs.cn)进行FPGA相关工程设计学习,也可以看一下我们往期的文章:

《基于FPGA的密码锁设计》

《波形相位频率可调DDS信号发生器》

《基于FPGA的曼彻斯特编码解码设计》

《基于FPGA的出租车计费系统》

《数电基础与Verilog设计》

《基于FPGA的频率、电压测量》

《基于FPGA的汉明码编码解码设计》

《关于锁存器问题的讨论》

《阻塞赋值与非阻塞赋值》

《参数例化时自动计算位宽的解决办法》

1.3 公司简介

明德扬是一家专注于FPGA领域的专业性公司,公司主要业务包括开发板、教育培训、项目承接、人才服务等多个方向。

点拨开发板——学习FPGA的入门之选。

MP801开发板——千兆网、ADDA、大容量SDRAM等,学习和项目需求一步到位。

网络培训班——不管时间和空间,明德扬随时在你身边,助你快速学习FPGA。

周末培训班——明天的你会感激现在的努力进取,升职加薪明德扬来助你。

就业培训班——七大企业级项目实训,获得丰富的项目经验,高薪就业。

专题课程——高手修炼课:提升设计能力;实用调试技巧课:提升定位和解决问题能力;FIFO架构设计课:助你快速成为架构设计师;时序约束、数字信号处理、PCIE、综合项目实践课等你来选。项目承接——承接企业FPGA研发项目。

人才服务——提供人才推荐、人才代培、人才派遣等服务。