本文为明德扬原创文章,转载请注明出处!

一、项目背景

二、硬件原理

2.1碲锌镉(CZT)探测器碲锌镉晶体

是一种性能优良的核辐射探测器材料,对X、γ射线有很高的探测效率和很好的能量分辨率,而且可以在室温下工作。对于碲锌镉核辐射探测器。当X、γ射线等高能粒子射线打入探测器的介质晶体时,射线粒子会与介质晶体中的原子产生能量交换,使射线很快损失掉一部分能量,这部分能量被晶体中的原子所吸收,促使其电子从满带跃迁到导带上,从而在导带产生电子,在满带剩余空穴,这便形成了可以用来形成电信号的电子-空穴对。在介质晶体的两端电极上加一高压外加电场,在高压电场作用下介质晶体内部的电子-空穴对分别向两端电极漂移,电信号通过电极被收集起来,在两端电极上形成微弱的感应电流。当前,碲锌镉探测器两个重要发展方向是:多块大体积并行探测器和面元阵列探测器。前者由多块体积大于1cm的碲锌镉晶体阵列组成,这类探测器解决了单个探测器体积小,总探测效率低的缺点,大大缩短了测量时间,尤其适于便携式谱仪系统,可应用于环境、港口、铁路货物等的放射性监测。后者是由碲锌镉晶体面元阵列组成,主要应用于核医学、天体物理等领域的能谱成像。本项目采用的是碲锌镉晶体面元阵列作为前端传感器。

2.2电荷积分放大器原理

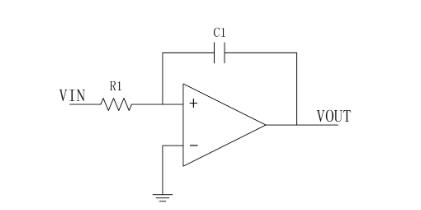

图1为运放积分放大器的电路图

图1理想积分放大器电路图

根据运放虚短可知,反向端与同相端电压相等,又由虚断可知,通过R1的电流与通过C1的电流相等。通过R1的电流为:

由此可得,运放的输出电压等于对输入电压在时间上的积分。若输入端为电荷采集装置的话,那么运放的输出与输入端的电荷量成正比。两部分组合起来就是电荷积分放大器。

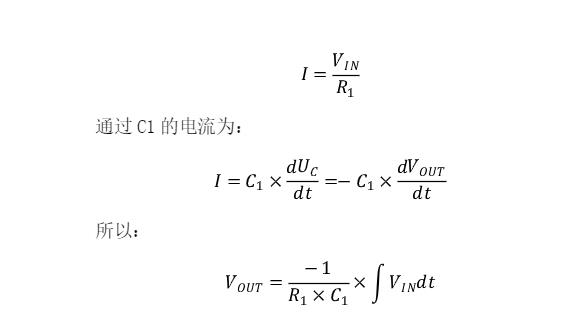

2.3AD8488简介

AD8488是一款128通道模拟前端,为高性能数字X射线系统而设计。它的模拟通道由一个积分器和增益可选的单端转低阻抗差分输出组成。该模拟通道将X射线或光电二极管检波器收集的电荷转换成电压信号。通道由CMOS晶体管组成,这些晶体管采用典型高输入阻抗的CMOS门。该设备的积分器采用一系列可选电容值,产生与电荷有关的电压,可适应广泛的输入电荷值。单端输入转差分输出电压放大器位于积分器之后,在这里偏移和低频噪声电压从输入电压中减去。一条128:1通道差分MUX位于缓冲器之后,驱动模拟输出缓冲。同时还提供开关驱动器和某些数字计时功能;这些功能全部集成在255引脚BGA基板上。全部128通道的电荷转换是同步进行的,之后便采用7位地址编码生成顺序电压输出读数。一共两次序列,对全部128通道进行采样。逻辑控制输入CS_A和CS_B分别选择通道地址的下限和上限64模块。

2.4AD8488工作原理

AD8488电路结构如图2所示:

图2AD8488电路结构图

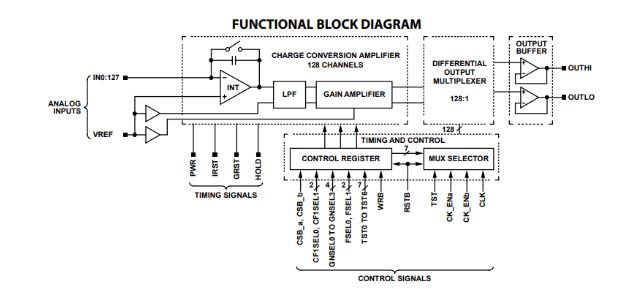

如图所示,AD8488主要由四部分构成。分别为前置电荷量转换器、差分输出选择器、输出缓冲器和时序/控制部分。前置电荷量转换器为128通道电荷积分放大器,每一个通道由一个放大器,一个低通滤波器和一个二级放大器构成。电路结构图如图3所示:

图3电荷量转换器结构图

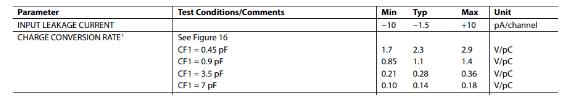

前端采集到的电荷信号通过第一级积分放大器进行转换,共有四档可选。各档位转换参数如图4所示:

图4电荷积分放大器转换参数

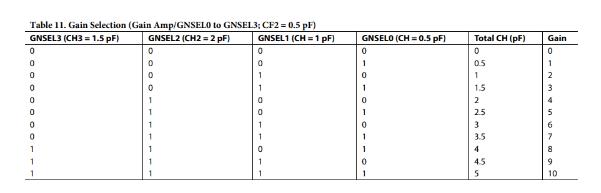

这四档分别由四种不同容值的反馈电容(CF1)控制。当CF1=0.45pF时,输出典型值为2.3V/pC(单位为伏特每皮库伦,指每积分1皮库伦,输出为1V。1pC=C);当CF1=1.1pF时,输出典型值为1.1V/pC,以此类推。CF1容值越大,增益越低。第二级低通滤波器实际上是一个保持装置,由一个电阻R1和一个电容构成。第一级放大器输出的电压信号通过R1给电容充电,以便于第二级放大器对进行积分放大。因此相当于一个低通滤波器。的参数由GNSEL[3..0]选择,参数如图5所示:

图5参数选择表

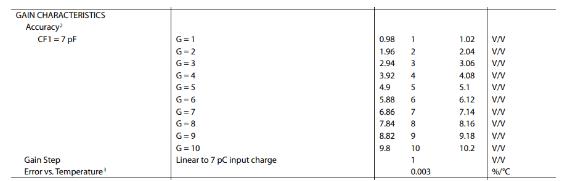

注:GNSEL[3..0]寄存器只能选择的容值,并不代表增益。上图中所表示的增益实际上是当二级放大器的反馈电容为0.5pF是,不同的容值下对应的增益。第三级放大器与第一级相同,也是一个电荷积分放大器。只不过第一级输出的电压信号是对芯片输入的电荷量的积分,然后该电压信号对第二级的电容进行充电,之后通过第二级放大器对的电荷量积分,最终输出新的电压信号,形成二次放大的效果。第二级积分放大器增益由CF2控制,共有10档,增益单位为V/V。注:因为第一级放大器已经将电荷信号转换为电压信号,因此第二级放大器的电压为伏特每伏特。增益表如图6所示:

图6第二级积分放大器增益表

2.5AD8488的控制时序

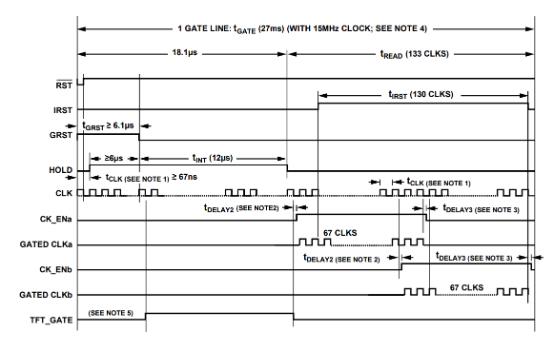

图7AD8488控制时序图

AD8488的控制时序如图7所示。主要控制信号如下:

- SWIRST是指IRST,用于控制第一级积分器的开关

- GNSEL0~3,用于控制中间部分的开关,0~3是并行的关系

- SWHOLD是指HOLD信号,用于控制通路

- SWGRST是指GRST信号,用于控制增益放大器的部分。

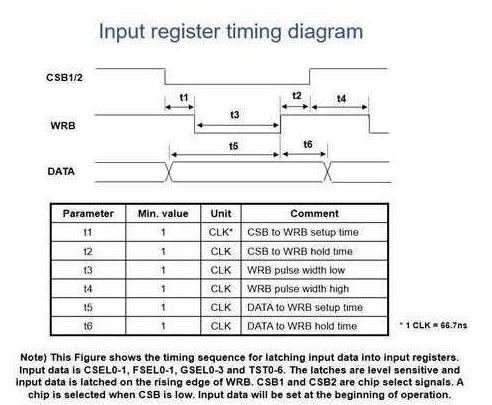

图8AD8488控制寄存器时序

2.6信号采集

信号采集部分使用了AD9244模数转换器,该芯片是一款65MSPS,14bit的ADC芯片。AD9244电路原理图如图9所示:

图9AD9244原理图

信号输入采用直流耦合的方式,为了防止9244输入饱和,将R6和R7改为1k。8488输出共模电压为2.048V,9244与8488共用同一个参考电压,因此9244的零点即为8488的零点。

三、软件设计

3.1FPGA工程架构

FPGA工程架构如图10所示:

图10FPGA工程架构

3.2FPGA工程功能

- 上位机或者硬件信号控制ad8488芯片的采集使能和复位,打包ad采集128通道的所有数据,并通过网口传输到上位机。

- 上位机可配置ad采集的帧数量、每帧采集轮次、各通道采集数据阈值;

- 上位机可配置ad8488芯片采集时序和采集增益;

- 上位机可配置重读包文序号和重读使能,支持重读每次采集的任意AD数据包文;

- 每采集完一帧数据就向上位机发送该帧数据的所有包文;

- AD采集数据为0xff时替换为0xff(通道数据间的分隔符是0xff避免采集数据和分隔符混淆)。

3.3模块介绍

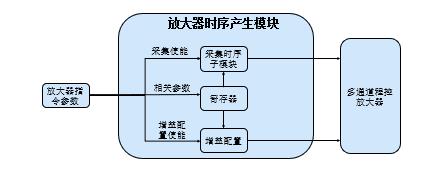

FPGA工程共分为四个模块,分别是放大器时序产生模块、采集

数据处理模块、采集帧标识产生模块、指令解析模块,各模块框图如

下:

-

放大器时序产生模块放大器时序产生模块根据参数和放大器控制逻辑生成放大器控制和增益配置时序。

-

采集数据处理模块采集数据处理模块用于切除8488时序中不需要的ADC数据;根据8488时序,对应通道与ADC数据;不同通道之间添加分隔符;一帧数据采集完成后添加帧标识标签。

图12采集数据处理模块

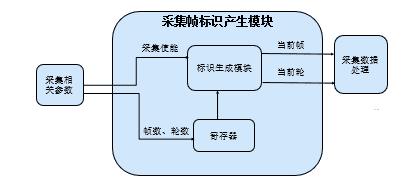

- 采集帧标识产生模块采集帧标识产生模块根据时钟计算当前帧和当前轮。

图13采集帧标识产生模块

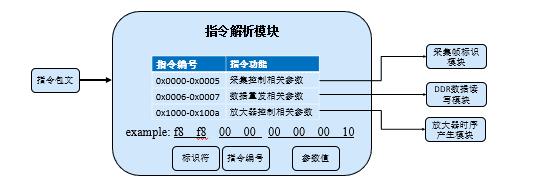

- 指令解析模块指令解析模块用于解析上位机下发的指令。指令格式数据长度短,需在包文后面补一定数量的0x00,避免包文过短被路由器丢掉。

图14指令解析模块

四、总结

4.1、系统改用锂电池进行供电,直接排除工频干扰。目前测试系统ADC底噪仅4bit,符合项目需求。

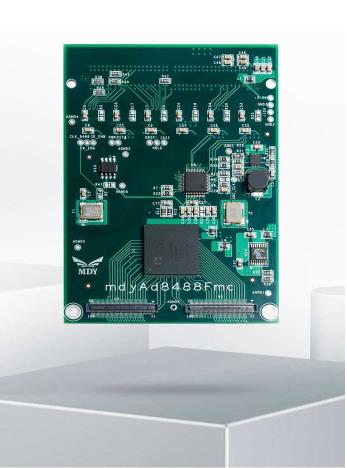

4.2、在数据处理时加入50Hz陷波处理。优点是硬件灵活,不需要硬件滤波。目前该采集系统已经设计成FMC子卡的形式,如图15所示。该子卡配合明德扬MP5620开发板,即可实现128通道电荷采集功能,可以用来进行工程验证,减少前期试错成本。

图15AD8488FMC子卡

温馨提示:明德扬除了培训学习还有项目承接业务,擅长的项目主要包括的方向有以下几个方面:

1. MIPI视频拼接

2. SLVS-EC转MIPI接口(IMX472 IMX492)

3. PCIE采集系统

4. 图像项目

5. 高速多通道ADDA系统

6. 基于FPGA板卡研发

7. 多通道高灵敏电荷放大器

8.射频前端

需要了解相关信息可以联系:吴老师18022857217(微信同号)