本文为明德扬原创文章,转载请注明出处!

1 AD/DA子板简介

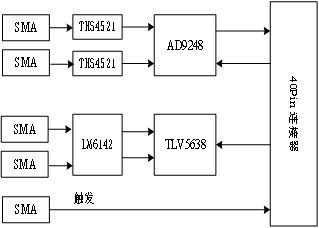

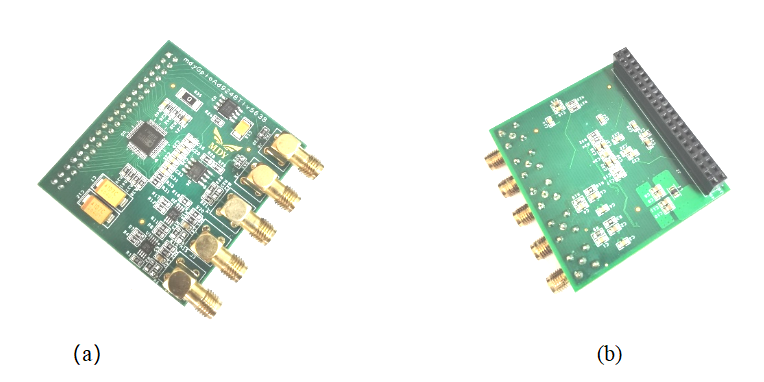

深圳明德扬科技教育有限公司(简称MDY)研发了一款低成本的AD/DA子板模块,命名为mdyGpioAd9248Tlv5638,该子板放置了一个两通道的ADC (AD9248)和一个两通道的DAC (TLV5638),mdyGpioAd9248Tlv5638子板模块规格如表一所示。AD/DA子板的原理框图如图1所示。AD9248的模拟输入为SMA同轴连接器,经过单端转差分后送入AD9248。DAC的两路模拟输出经过运放跟随后连接到SMA。触发信号同样通过SMA输入。AD9248的数字输出、时钟信号,TLV5638的SPI控制信号以及触发信号连接到间距2.54mm的40Pin连接器上。整个子板模块供电3.3V。实物图正面如图2(a)所示,实物图背面如图2(b)所示,尺寸56 mmÍ52 mm。

表一 mdyGpioAd9248Tlv5638子板模块规格

ADC

AD9248 采样率65MHz,14位

DAC

TLV5638,12位

THS4521

LM6142

3.3V

差分运放

运放

工作电压/最大电流

模块尺寸、工艺

56*52mm、沉金工艺

工作温度

-40°C~+85°C

图1 AD/DA子板模块的结构示意图

图2 (a) AD/DA实物图正面,(b)AD/DA实物图背面。

2 mdyGpioAd9248Tlv5638子板模块详细介绍

2.1 AD9248芯片

AD9248是一款双核、3 V、14位、20/40/65 MSPS模数转换器(ADC),集成了两个高性能采样保持放大器和一个基准电压源。它采用多级差分流水线架构,内置输出纠错逻辑,在最高65 MSPS数据速率时可提供14位精度,并保证在整个工作温度范围内无失码。利用宽带宽、差分采样保持放大器(SHA),用户可以选择包括单端应用在内的各种输入范围和偏移。该器件适用于各种应用,包括在连续通道中切换满量程电平的多路复用系统,以及采用远超过Nyquist速率的频率对输入进行采样。AD9248适用于通信、成像和医疗超声等应用。采用双单端独立时钟输入来控制所有内部转换周期。AD9248-65提供一个占空比稳定器(DCS),可用来补偿较大的时钟占空比波动,使转换器保持出色的性能。数字输出数据格式为标准二进制或二进制补码。超量程信号表示溢出状况,可由最高有效位来确定是下溢还是上溢。AD9248采用先进的CMOS工艺制造,提供节省空间的64引脚LQFP封装,额定温度范围为-40°C至+85°C工业温度范围。AD9248的结构示意图如图3所示。

图3 AD9248的结构示意图

图3 AD9248的结构示意图

本模块中ADC选用的采样率为65 MSPS,参考电平选用内部1 V参考电平,输入模拟差分信号范围是2 Vpp,共模电平为1 V。

2.2 TLV5638

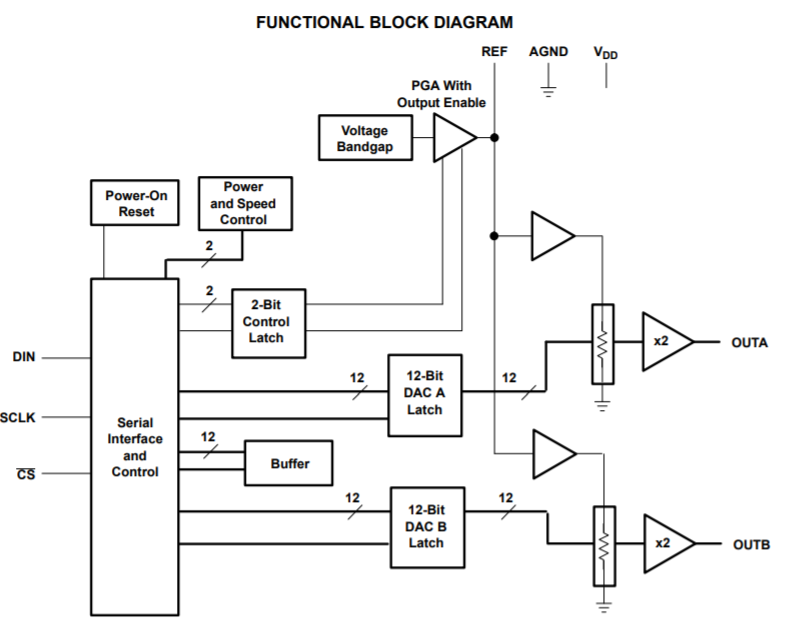

TLV5638是一个双12位电压输出DAC,具有灵活的3线串行接口。该串行接口允许与TMS320、SPI™、QSPI™和Microwire™串行端口的直接相连。它被编程为一个16位的串行数据,包含4个控制位和12个数据位。电阻串的输出电压由一个X2增益轨至轨输出缓冲器缓冲。该缓冲器具有AB类输出级,以提高稳定性和减少沉淀时间。数模转换器的可编程时间使设计者能够优化速度与功耗。凭借其片上可编程的精密电压基准, TLV5638简化了整个系统设计。由于它能够提供高达1 mA的电压源,因此该基准也可作为系统基准使用。该器件采用CMOS工艺,设计用于2.7 V至5.5 V的单电源工作。8引脚SOIC封装,以减少在标准商业、工业和汽车温度范围内减少电路板空间。TLV5638的功能框图如图4所示。

图4 TLV5638的功能框图

本模块中DAC参考电平选用内部1.024V参考电平,输出模拟信号范围是0-2V。

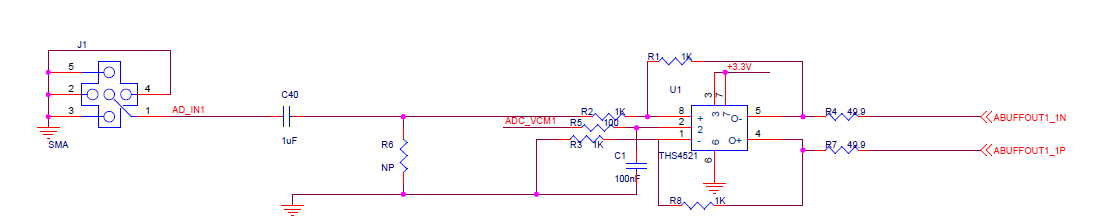

2.3 THS4521

THS4521器件具有非常低的功耗、全差分轨到轨输出的运算放大器,带宽:145 MHz(AV = 1 V/V)。输出可以共模控制(带低偏移)。供电电压 +2.5 V (±1.25 V) 到 +5.5 V (±2.75 V)。本模块中共模输出电压设置为1 V,与ADC完美匹配。THS4521电路如5图所示。

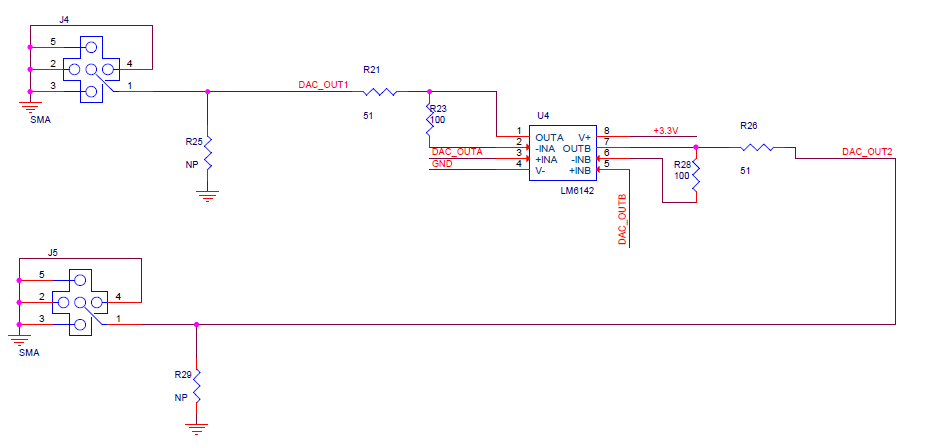

2.4 LM6142

LM6142同样为轨到轨输出的低功耗两通道运算放大器,供电电源从1.8V到24V,带宽17MHz。选用LM6142主要对DAC输出进行缓冲增加驱动能力。LM6142电路如图6所示。

图6 LM6142电路图

2.5 触发信号

模块上放置了一个SMA接口,直接连接到40 Pin连接器上,与主板上的FPGA相连,可以给系统接收外部触发信号。该触发信号的原理图如图7所示。

图7 触发信号原理图

2.6 连接器管脚定义

该子板模块上与FPGA通信的是一个40 Pin 间距2.54mm 连接器插座,AD9248的数字输出、时钟信号,TLV5638的SPI控制信号以及触发信号连接到该连接上。

1 总结

深圳明德扬科技教育有限公司研发的mdyGpioAd9248Tlv5638子板模块,是一个低成本的AD/DA模块,该子板上具有一个AD9248芯片和一个TLV5638芯片,对于二次开发来说,非常适合。

温馨提示:明德扬除了培训学习还有项目承接业务,擅长的项目主要包括的方向有以下几个方面:

1. MIPI视频拼接

2. SLVS-EC转MIPI接口(IMX472 IMX492)

3. PCIE采集系统

4. 图像项目

5. 高速多通道ADDA系统

6. 基于FPGA板卡研发

7. 多通道高灵敏电荷放大器

8.射频前端

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

需要了解相关信息可以联系:吴老师18022857217(微信同号)