PCIE 上位机 介绍

本文为明德扬原创文章,转载请注明出处! 作者:云哥哥

开发环境:windows开发平台:QT5.11.3

1、PCIE上位机测试过程

FPGA将数据传到芯片中,通过pcie再将芯片算完的数传给上位机。目标:

1.实现上位机的速度测试,经测试pcie的传输速度达到2.2GB/s以上

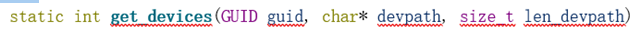

2.上位机收到pcie的数据后保存在D盘的根目录下,pcie实现测速的原理:首先,打开上位机后先检测pcie设备是否已经准备好,调用的函数为

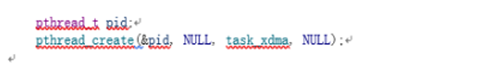

若pcie init()<0,则检测不到pcie设备。检测完准备好后,开启一个线程检测接收的数据;开启线程的函数如下:

线程不断读取的函数如下:

其中,c2h_transfer_size:每次读取的长度为8MB

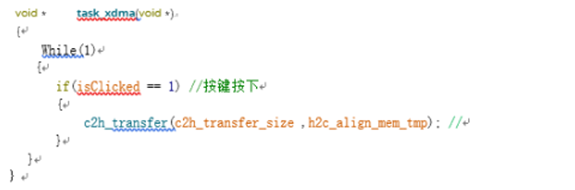

H2c_align_mem_tmp:读取到的数据保存在这块内存中检验上位机收到的数据是否正确。由于要检测数据所以可以暂时把数据保存在文件中,保存的文件的函数如下:

File_test。Close()://关闭文件,刷新数据当用户想保存文件的时候调用以上代码即可

2、 分析文件

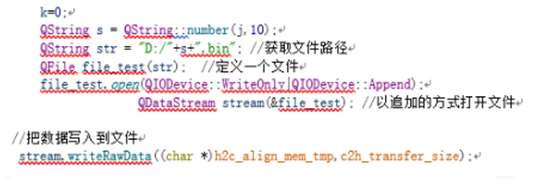

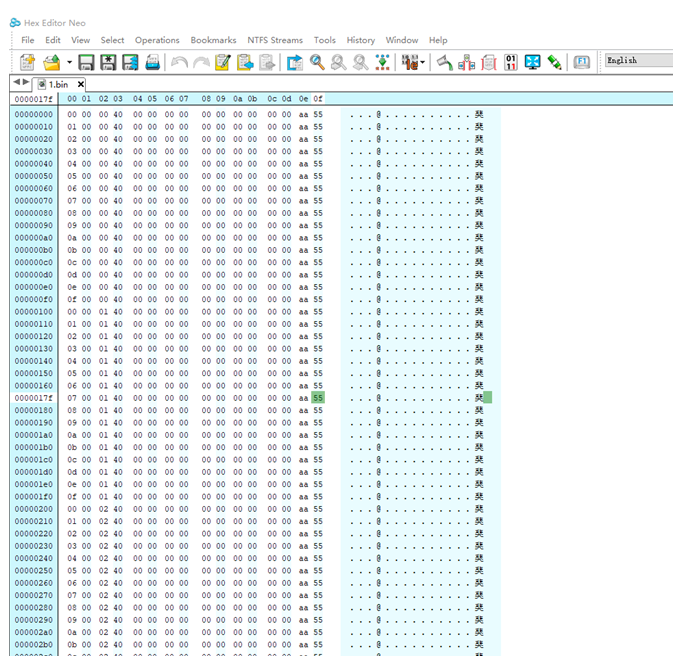

保存的文件是以Bin格式保存的,可以使用Hex Editor ,打开文件如下:

当用户相分析数据的时候可以使用Matable或者qt程序自行写软件分析这里,我们明德扬的pcie自定义了一个数据包,包的格式是以16个字节为一个数据,data[16]={0X55,0XAA,0X00,0X00,0X00,0X00,0X00,0X00,0X00,0X00,,0X00,0X00,0X40,0X02,0X00,0X01}

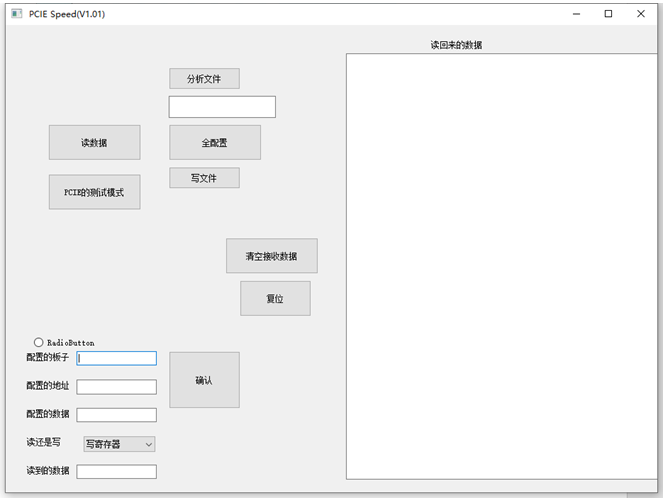

其中0X55,0XAA是包头,,0X40,0X02是包序列,0X00,0X01包数据当包数据0X00,0X01递增到0X00,0X0F后,然后归为0X00,0X00,包序列也递增,如0X40,0X00递增到0X40,0X01.然后用qt测试,打开如下界面:

然后点击“读数据”,数据保存在D盘,然后打开如下图片中pcie_fun.c文件,该文件是pcie驱动文件

里面

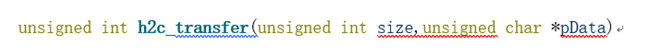

是设备输出上位机往fpga发送数据的函数

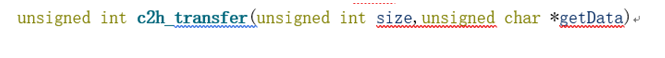

上位机接收fpga的数据的函数

以上为pcie 上位机的介绍,感兴趣的同学可以加Q:1465617980 云哥哥 了解更多的学习信息。