SDRAM的硬件解读(个人总结版)

本文为明德扬原创文章,转载请注明出处!作者:张先生

在FPGA中我们经常会用到SDRAM做数据缓存,比如我们收到一副图像时,由于FPGA的内部的RAM不够,此时我们就可以将数据存在SDRAM里面,等到我们需要用的时候再从SDRAM里面把图像取出来进行显示;那么今天我们就对SDRAM的硬件进行讲解,先不解释SDRAM的原理,这里我们来循序渐进的学习如何使用SDRAM。

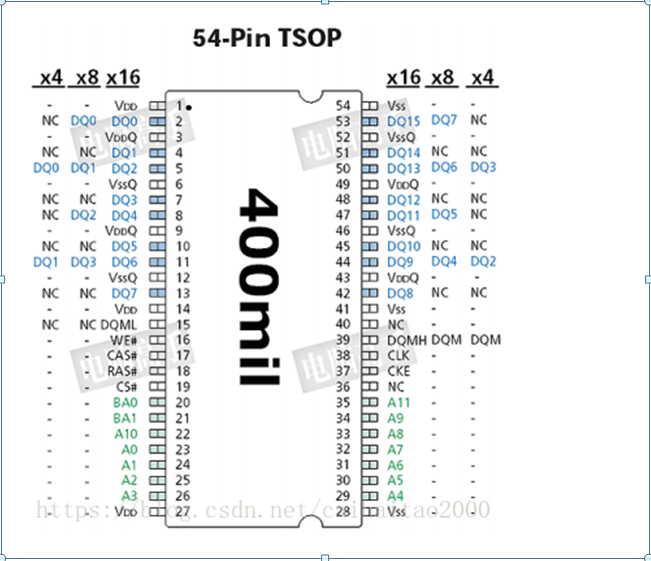

一、SDRAM管脚解释

首先对SDRAM进行硬件电路上的分析,我们要弄明白的SDRAM的各个管脚都表示什么意思,下图是某个芯片SDRAM的管脚图。

1.VDD、VDDQ、VSS、VSSQ

电源VDD和VDDQ这里就不过多解释了,至于供电电压是多少,可以具体去查看一下电路原理图。VSS和VSSQ,一般表示地信号,连接电路板的地。

2. A0------A10、DQ0----DQ15

着重要注意的是A0------A10以及DQ0----DQ15,我们首先来弄明白这两组信号。A0----A10表示的地址线,DQ0-----DQ15表示的数据线,我们想一下,假设我们要存一段数据,肯定是把数据(DQ组的信号)存在某一个地方(A0到A10)。比如说我们可以把一组数据“0x0001 0x0002 0x0003 0x0004 0x0005 0x0006 0x0007 0x0008”依次存在SDRAM的地址“0 1 2 3 4 5 6 7 ”里面,当你要取数据的时候把“0 1 2 3 4 5 6 7 ”里面的数据读出来即可。

3.clk

用一个生活中用到的知识来理解,我们平常都会去买电脑,买电脑的时候我们会关注一个指标,CPU的频率是多少;同理的,SDRAM里面也是要有时钟才能运行的嘛,那么这个时钟要选取多少合适呢,我们一般要给它多少频率呢???200M ???100M???不卖关子了,这个指标一般数据手册上都有,但是数据手册上一般标的是最大的频率,比如说133MHz,那么当我们给SDRAM的时钟频率比手册上的标的最大的频率小的时候,如125MHz就是可以运行的。

4. BA0、BA1

BA0和BA1这两个是Bank。不要惧怕bank是什么,也没必要理解bank是什么意思,因为我们也不是设计SDRAM芯片的,我们只是运用SDRAM芯片的。什么是bank,通俗的讲,就是SDRAM芯片里面有多少个小块,BA0和BA1共有4个小块,很简单嘛2的2次方,假如说别的SDRAM里面有3个BA管脚,那么就是有2的3次方等于8个小块。它的作用说白了就是BA组(bank)信号和A0---A10(地址组信号)的组合组成了SDRAM的总的地址。

5. DQM

假设你是一个很细心的人你会发现DQ(数据组)的信号有16根,也就是说两个字节,但是有没有这样一种情况,我们还剩一个单字节的数据的时候怎么到SDRAM,筹不够两个字节啊。这时DQM信号就体现出它的作用了,当给DQM的高位为1,就表示存进SDRAM里面的数据高字节无效;同理低位为1,表示那么存进SDRAM的低字节无效,说白了就是数据屏蔽位。

6.CS

CS为片选,你的FPGA里面有可能挂着不止1片SDRAM,这时你要操作哪一个SDRAM那就选中它,就是这么容易理解。

7. WE、CAS、RAS、CKE

WE、CAS、RAS、CKE它们四个组合成了一个命令的控制,为什么要用命令,我们一起来思考下。SDRAM只是一片芯片,它不可能知道我们人的思想,也不知道我们是要对它写还是要对它读。我们写驱动的时候是不是要告诉我要往你SDRAM里面写数据了,怎么告诉它?肯定给它一个命令指示,SDRAM只有收到命令的时候它才能知道你想要数据,好让它准备准备。同理当我们要从SDRAM里面读数据的时候肯定也要给它命令,让SDRAM知道我们要读数据,这就是我们的命令的作用了。那么你有可能会有个疑问,SDRAM不就是有写命令和读命令就行了,为什么要这么多根线组成呢?其实不是,SDRAM里面的命令有很多,具体的我们可以去查看收据手册里面的命令表学习。

二、原理图和PCB

下面我们来讲原理图和PCB。就本人用过的,如说明德扬使用的W9864,电源我们提供给SDRAM用电源为的3.3V,其它的什么数据线、地址线、BANK线、命令线等直接连接到FPGA也可,但是最好连接到同一个FPGA的bank。有可能有的人觉得不重要,虽然SDRAM有可能是不重要,但是如果是DDR2和DDR3的时候就显得很重要了,DDR2和DDR3是要接到FPGA的特定的管脚才行的,不是说我们想接到哪都可以,所以在画DDR2和DDR3的时候要先进行FPGA工程的编译,先确定好管脚的位置。

回到我们的SDRAM,刚才我们说的SDRAM的时钟线。那么时钟线能不能连接到FPGA的普通管脚?答案是可以的,但是我们不建议那么做,一般来说呢,可以连接到FPGA的某一个时钟输出管脚,因为本来输出的就是时钟信号。

再来说说PCB。SDRAM的对PCB的要求高不高呢?按照数据手册的理论一般都是要求你对SDRAM做50欧姆阻抗匹配和等长,有的工程师有可能忘了做阻抗匹配了也没做等长那怎么办,样板已经回来了,会不会有问题呢?小平同志有句话说的好,实践是检验真理的唯一标准!我可以大胆的告诉你,SDRAM哪怕忘了做阻抗,问题也是不大的,最起码样板是可以调出来,第二版的时候再做也是可以补救的。当然我们不是叫你不去做阻抗哦,只是说不做也能调试出来罢了。

以上就是我从实践中总结出的SDRAM硬件解读,大家可以在下方留言互相学习交流!