本文为明德扬原创文章,转载请注明出处!

很多朋友在工程模块划分的时候总会遇到很多问题,比如不知道如何下手、模块划分不合理等;我开始也是这样的,在学习了明德扬的几项工程以后,按照老师分享的思路,也对模块划分有了一定的小经验,今天通过案例的方式与大家分享。

今天分享的案例是千兆以太网工程。该工程是明德扬的网络班、就业班的其中一个项目,涉及到MAC协议、ARP协议、IP协议和UDP协议的实现,协议较多,划分的模块也较多。

一、模块划分要点总结

1、列出项目的功能要求(客户提出的产品功能要求)

2、画出硬件的系统结构框图(添加外设)

3、框图中每个外围接口都对应有一个接口转换模块

接口转换模块的作用是将外围器件的接口时序转为通用的接口时序,或者将通用接口时序转换为外围器件接口时序,这样使得FPGA内部其他模块不用再关心外围接口的时序了。

MDY规范通用接口时序:

l data以及对应的vld,传输单个数据格式

l MDY的包文格式,din,vld,SOP,EOP,MTY,ERR

l wren,waddr,wdata;rden,raddr,rdata,rdata_vld

4、考虑是否涉及指令系统(操作码+数据格式)

上位机,例如PC,ARM,DSP或者其他的器件,只涉及到一个接口,但是却有很多指令或者命令功能要发送,因此就需要一个指令系统。

指令系统一定会涉及到命令、地址和数据。这种情况,肯定会有一个“寄存器解析模块”,根据命令、地址和数据,改变相应的寄存器的值。

5、考虑外围器件是否涉及寄存器配置

项目中有某些外设,上电工作前需要进行配置才能按要求工作。因此需要对外设内部寄存器进行读写,这一流程是通过FPGA来进行配置。

遇到这个情况,使用MDY推荐的模块寄存器配置结构:

寄存器配置表模块+寄存器读写配置模块+外设配置接口时序转换模块

6、根据实际情况,增加、补充或者拆分,优化对应模块,随时调整

原则:根据接口信号,看模块间是否方便对接。接口就决定了模块功能。所以在这一层的调整,一定要清楚接口的定义。

7、考虑是否涉及多路进一路出,要用FIFO

调度FIFO要考虑自身带宽能否满足多路一起突发发送时的数据量情况。如果带宽不满足,就要要输出给上游模块RDY信号。此时RDY信号有效取决于自己设置FIFO的Almost Full信号。如果带宽满足则不必设RDY信号。

8、考虑是否涉及到速率匹配问题,要加上RDY信号或者FIFO

首先考虑与外围器件通信的接口上是否需要rdy信号(FPGA内部运行频率往往与设接口速率不一致),然后考虑FPGA内部模块间数据带宽是否不一致,有等一等的情况。

二、千兆以太网工程案例分析

根据前面总结的要点,通过实际项目案例来分析一下FPGA内部功能模块是怎样划分的。这里我们选取已经做过的千兆以太网工程,接下来按照上面总结的模块划分步骤,一步步完成模块初步划分!

1.列出项目的功能要求

本项目功能要求:FPGA内部产生要发送的包文数据,通过UDP协议,发送给PC;PC发送UDP格式包文数据,FPGA需要解析UDP协议,提取出用户数据;ARP协议实现定期发送ARP协议,获取对方电脑的物理地址。

功能分析:

a) FPGA内部产生发送的包文数据;

b) 要通过UDP协议发送,就需要添加MAC协议头部,IP协议头部,UDP协议头部;

c) FPGA接收到PC发来的UDP报文,要一层层解析协议头部信息,先解析出MAC头,然后是IP头,UDP头,最后才能获取用户数据;

d) FPGA定期发送ARP协议请求报文;

e) FPGA接收到PC发来的ARP协议应答报文,要解析出源MAC地址;并在发送包文数据中,将获取的MAC地址作为目的MAC地址进行打包发送。

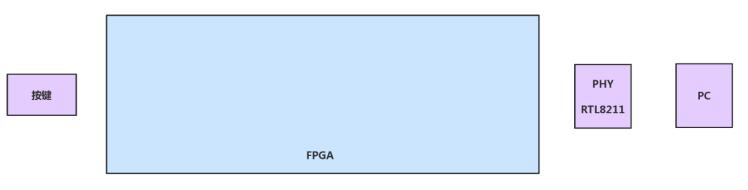

2.画出硬件系统结构框图

根据步骤1总结出的功能要求,找到除FPGA外需要哪些外围器件。分析得出:

FPGA与PC通信是以千兆以太网的形式,需要将FPGA输出的信号调制成千兆以太网信号,本项目选取了外部PHY芯片RTL8211来实现此通信调制功能。同理PC端发送的数据通过千兆以太网网线传输,需要经过PHY解调后输出给FPGA;

为了设计方便,FPGA发送的报文数据中,完成FCS校验的计算交给了MAC IP核来完成;同理,接收端接收到PC发来的报文数据也由MAC IP核完成FCS校验;

前期为了验证设计,考虑添加按键作为触发MAC IP核初始化的启动条件。

外围器件总共需要三个:

a) 按键

b) 2PHY(RTL8211)

c) 3PC

画出系统框图如下所示:

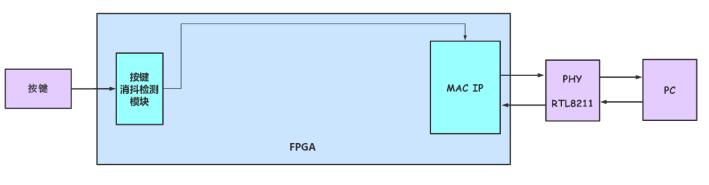

3.框图中每个外围接口都对应有一个接口转换模块

a) 按键对应的接口转换模块是按键消抖检测模块;

b) PHY对应的接口转换模块是MAC IP核模块。

添加后框图如下所示:

4.考虑是否涉及指令系统

本项目不涉及指令系统

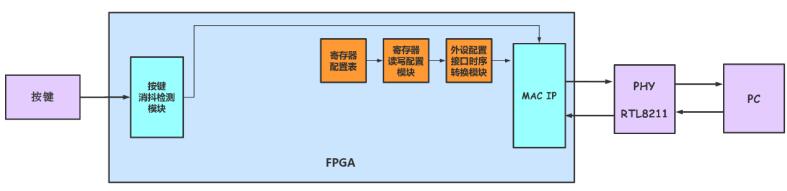

5.考虑外围器件是否涉及寄存器配置

本项目中MAC IP核涉及寄存器配置。使用MDY推荐模板:寄存器配置表模块+寄存器读写配置模块+外设配置接口时序转换模块;

由于MAC IP配置接口使用的是Avalon协议(与MDY接口协议不同之处在于waitrequest信号),所以外设配置接口时序转换模块对外接口也应该是Avalon,对内则是MDY规范接口。

完善后如下所示:

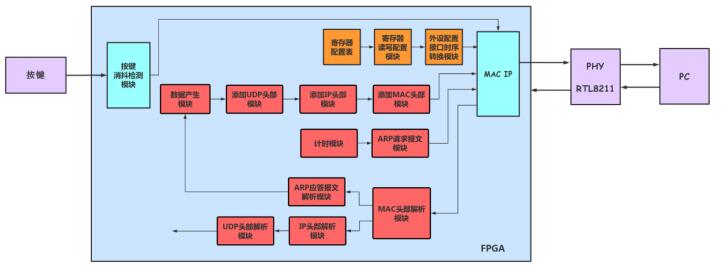

6.根据实际情况,增加、补充或者拆分独立对应模块,随时调整

到第6步,根据数据流向,需要对模块间的接口进行详细分析了,补充模块或者将功能相同的模块合并化简。

从发送侧数据流向思考:

a) FPGA内部产生要发送的数据,因此需要一个数据产生模块;

b) 产生的发送数据需要先添加UDP头部,所以需要一个添加UDP协议头部模块;

c) 然后添加IP头部,需要一个添加IP协议头部模块;

d) 最后添加MAC头部,就完成了完整的发送UDP协议报文,因此需要一个添加MAC协议头部模块;

e) 同时需要定期发送ARP协议请求报文,需要一个ARP请求报文模块;

f) 由于ARP报文需要定时产生,所以需要一个计时模块。

从接收侧数据流向思考:

FPGA接收到PHY解调出的PC发送来的UDP报文或者ARP应答报文,经过MAC IP核验证FCS后,解析出正确或者错误的UDP、ARP报文:

a) 经过MAC IP核输出的报文需要进行MAC头部检查,正确则输出UDP、ARP报文,错误则做丢包处理。所以需要一个MAC头部解析模块;

b) 经过MAC头部解析模块处理后输出的是正确的IP报文,此时需要进行IP头部检查,正确则输出报文,错误则做丢包处理。所以需要一个IP头部解析模块;

c) 经过MAC头部解析模块处理后输出的是正确的ARP应答报文,此时需要进行ARP报文解析,获取发送端MAC地址。所以需要一个ARP应答解析模块;

d) 同1、2两步原理,输出UDP报文需要进行UDP头部检查,所以需要一个UDP头部解析模块。

经过UDP头部解析模块解析出来的报文数据即是PC端发来的正确用户数据,输出即可。

补充后如下图所示:

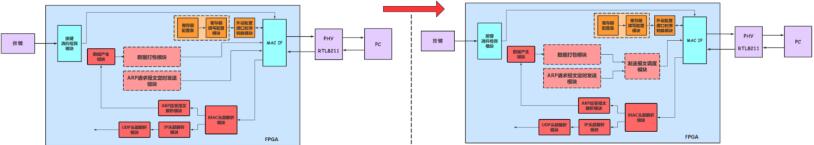

接下来将功能互斥、数据流向相关,接口一致的模块做合并化简处理,如下图所示:

7.考虑是否涉及多路进一路出,要用FIFO

本项目数据流方面涉及多路进一路出的问题。

在进行模块优化时,注意到产生的用户数据和定时ARP请求报文不能同时输出给MAC IP核,需要一个发送调度模块来完成多路输入一路输出的调度,是发送打包模块送来的UDP报文还是发送ARP请求报文。

8.考虑是否涉及到速率匹配问题,要加上RDY信号或者FIFO

首先考虑与外围器件通信的接口上是否需要rdy信号。

外围PHY芯片与FPGA通信是经过MAC IP核来处理,时序MAC IP核已经做好了,所以不需要设rdy信号。

再考虑FPGA内部模块间运行速率不匹配的情况,根据数据流方向来考虑:

发送侧:

a) 发送报文打包模块需要时间(计算各个协议头部校验和,长度等信息),所以需要在数据产生模块和数据打包模块间设FIFO并设rdy信号。

b) 数据打包模块和ARP请求报文发送模块同时发送给报文调度模块,发送包文调度模块不能同时响应,需要FIFO来缓存,考虑到突发情况FIFO会溢出,所以需要与数据打包模块和ARP请求报文定时发送模块间设FIFO并设RDY信号。

接收侧:

接收侧模块间速率匹配,不需要设FIFO和RDY信号。

最终得到的模块图如下所示:

到此,根据模块划分步骤一步步做下来,千兆网工程的模块划分雏形初步已经完成。具体实践中需要根据FPGA内部信号的调整,随时拆分或独立来增减功能模块。

以上就是我们做模块划分的基本思路,大家有什么问题可以加Q群544453837进行交流,更多FPGA相关资料可以登录明德扬论坛进行学习讨论:http://www.fpgabbs.cn/!