明德扬科教推出的FPGA系列教学视频中,点透学习误区,拨出设计精髓,是明德扬点拨FPGA入门大串讲的核心思想,明德扬根据丰富的项目经验和教学经验,手把手教FPGA学习爱好者开发各种模块,从信号的定义,结构划分,代码编写,仿真测试以及最后的上板调试,让视频学习的你亲身经历模块开发的全部过程。教学充分结合项目实践,在实现功能的同时,注重效率,成本和质量。教程既包括简单的模块设计,如跑马灯、秒表,也包括复杂的系统设计,如IP协议栈的实现等,从入门、提高到精通,满足不同层次学生的学习需求。

入门大串讲视频主要包含六方面的内容,第一部分是讲述大部分同学经常进入的学习误区。第二部分内容是FPGA的所有知识点。第三部分是分别讲述四方面的内容,包括:组合逻辑,D触发器,时序逻辑和FPGA时序四大知识点的概述。今天主要是点透学习FPGA容易进入的五大误区。

误区一:花大量时间学习verilog语法

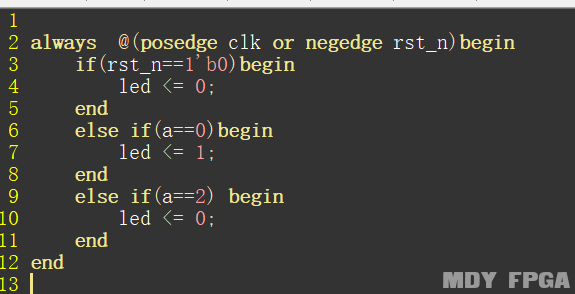

很多同学入门的时候就是看verilog,甚至很多同学花了几个月时间用来学习语法。其实,verilog里边的语法,90%的是用来测试用的,我们在设计的时候仅仅用了10%的代码。大家可以看一下明德扬的一个代码规范,我们的代码结构非常简单,语法也是非常简单,首先是例化的方法,还有各个always 语句,可以说,我们的语法里面几乎只是用到了if、else语句,这已经足够应付我们大部分场合。所以,我们学习语法不需要那么多时间。

误区二、软件思维,习惯把verilog当C语言使用

还有一种误区就是把verilog当C语言使用,很多同学都具有软件思维,不知道会综合出什么电路,甚至代码,设计代码里面含有initial,#5、还有for循环等语句,我们必须知道,verilog是硬件描述语言,不是设计语言。这就是说,我们在做一个FPGA设置之前,其实已经有硬件的电路结构在头脑里面,我们只是用 verilog 把它描述出来而已,而不是用 verilog 去设计一门电路出来。

很多同学会问,学了C语言之后,学 verilog是不是很容易?其实从明德扬的教学经验来看,学了C语言之后,学verilog是更加麻烦,这种思维很难转变。事实上,我们的思维是学了c语言之后,脑子就深深中毒了,满脑子的设计思维。

误区三、钻研verilog语法,追求用最少的代码实现功能

还有很多同学在学verilog语法,在钻研这个语法,他们追求是用最少的代码实现功能。其实,在FPGA里面,代码的代码量的多少不是一个衡量的标准,我们衡量设计的好坏不是看代码量,而是看综合出来的电路。比如说我们看,我们综合出来电路用了多少资源,我们的设计的电路能跑到多少多少兆,这才是我们衡量出来的标准,绝对不是一个代码量。如果你用1000行代码,是用1000行代码写出来电路非常好,那么这就是一个好的代码。在海思里面,我们甚至用这行为描述语言都不用,我们就只用那个门级电路去搭一个电路,那么这样就能保证出最好的一个时序,然后这就是一个最好的代码。

误区四、追求功能的实现

很多人在设计做一个电路设计或做实验的时候,只看功能实现没有,认为功能实现了就完成了设计。因此,他们不停的做I2C,做串行接口,又做跑马灯,又做数码管等很多实验,但是设计能力却提高的很慢。其实大家要相信一点,企业20%的时间是花在功能实践上,80%的时间是花在提高质量上。事实上,要实践功能非常容易,但是,要提高质量却非常之难。

误区五、认为FPGA逻辑设计很容易,算法实现才是高级的设计

认为逻辑设计很简单,那是因为标准很低,如果是高标准的功能实现,它应该有这样的体现:它能快速进行设计,综合出来的电路资源非常少,并且速率能满足我们的需求,可维护性强,可扩展性高,这要实现这样的高质量代码是非常难的。

以上几点都是很多同学入门学习FPGA时容易进入的误区,进入误区最大的弊端就是浪费时间,用过多的时间来学习没必要的知识,没有精简掌握学习的要点。明德扬推出的点拨FPGA之verilog快速入门这一门视频,用一个小时掌握verilog,这一小时足够掌握我们设计的需求。