本白皮书讨论各种存储器接口控制器设计所面临的挑战和 Xilinx 的解决方案,同时也说明如何使用 Xilinx软件工具和经过硬件验证的参考设计来为您自己的应用(从低成本的 DDR SDRAM 应用到像 667 Mb/sDDR2 SDRAM 这样的更高性能接口)设计完整的存

储器接口解决方案。

存储器接口趋势和 Xilinx 解决方案

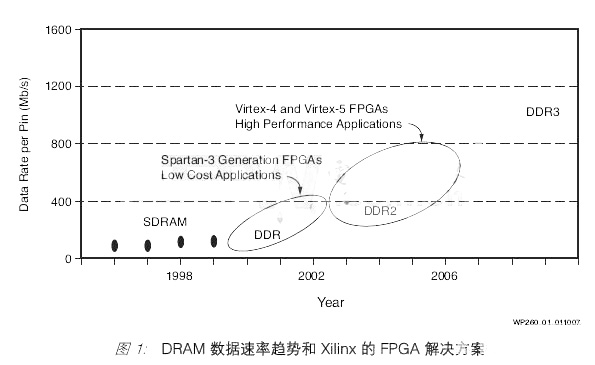

20 世纪 90 年代后期,存储器接口从单倍数据速率 (SDR) SDRAM 发展到了双倍数据速率 (DDR) SDRAM,而今天的 DDR2 SDRAM 运行速率已经达到每引脚 667 Mb/s或更高。当今的趋势显示,这些数据速率可能每四年增加一倍,到 2010 年,随着DDR3 SDRAM 的出现,很可能超过每引脚 1.2 Gb/s。见图1。

应用通常可分为两类:一类是低成本应用,降低器件成本为主要目的;另一类是高性能应用,首要目标是谋求高带宽。

运行速率低于每引脚 400 Mb/s 的 DDR SDRAM 和低端 DDR2 SDRAM 已能满足大多数低成本系统存储器的带宽需求。对于这类应用,Xilinx 提供了 Spartan-3 系列FPGA,其中包括 Spartan-3、Spartan-3E 和 Spartan-3A 器件。

高性能应用把每引脚 533 和 667 Mb/s 的 DDR2 SDRAM 这样的存储器接口带宽推到了极限;对于这类应用,Xilinx 推出了 Virtex-4 和 Virtex-5 FPGA,能够充分满足今天大多数系统的最高带宽需求。

带宽是与每引脚数据速率和数据总线宽度相关的一个因素。Spartan-3 系列、Virtex-4、Virtex-5 FPGA 提供不同的选项,从数据总线宽度小于 72 位的较小的低成本统,

到576 位宽的更大的 Virtex-5 封装(见图2)。

高于 400 Mb/s 速率的更宽总线使得芯片到芯片的接口愈益难以开发,因为需要更大的封装、更好的电源和接地-信号比率。Virtex-4 和 Virtex-5 FPGA 的开发使用了先进的稀疏锯齿形 (Sparse ChevrON) 封装技术,能提供优良的信号-电源和接地引脚比率。每个 I/O 引脚周围都有足够的电源和接地引脚和板,以确保良好的屏蔽,使由同步交换输出 (SSO) 所造成的串扰噪音降到最低。

温馨提示:明德扬除了培训学习还有项目承接业务,擅长的项目主要包括的方向有以下几个方面:

1. MIPI视频拼接

2. SLVS-EC转MIPI接口(IMX472 IMX492)

3. PCIE采集系统

4. 图像项目

5. 高速多通道ADDA系统

6. 基于FPGA板卡研发

7. 多通道高灵敏电荷放大器

8. 射频前端

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

需要了解相关信息可以联系:吴老师18022857217(微信同步)