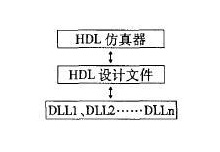

协同仿真就是利用仿真工具提供的外部接口,用其它程序设计语言(非HDL语言,如c语言等)编程,用辅助仿真工具进行仿真。Modelsim提供了与c语言的协同仿真接口。以Windows平台为例,用户可通过modelsim提供的c语言接口函数编程,生成动态链接库,由modelsim调用这些动态链接库进行辅助仿真,如图1所示。

图1 协同仿真示意图

2 Modelsim及FLI接口介绍

Modelsim是Model Technology(Mentor Graphics的子公司)的HDL硬件描述语言仿真软件,可以实现VHDL、Verilog以及VHDL-Verilog混合设计的仿真。除此之外,Modelsim还能够与c语言一起对HDL设计文件实现协同仿真。同时,相对于大多数的HDL仿真软件来说,Modelsim在仿真速度上也有明显优势。这些特点使Modelsim越来越受到EDA设计者、尤其是FPGA设计者的青睐。

Modelsim的FLI(Foreign Language Interface)接口,提供了c语言动态链接程序与仿真器的接口,可以通过c语言编程对设计文件进行辅助仿真。

3 协同仿真系统的结构及意义

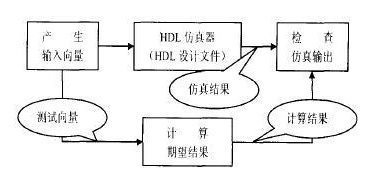

Modelsim与c语言协同仿真,一是用于产生测试向量,避免手工编写测试向量的繁琐;二是可以根据程序计算结果自动检查仿真结果正确与否;三是模拟其它模块(如RAM)的功能,在系统级对设计文件仿真。实践中一般是把一和二结合在一起,用程序产生仿真向量,一方面输出给设计文件作为输入,另一方面由程序本身对该向量计算,把得到的结果与仿真器的输出结果比较,检查逻辑是否正确,如图2所示。至于模拟功能,现在已经有一些通用芯片的模拟程序,如denali可以模拟RAM的功能。另外,用户也可以利用modelsim提供的编程接口自己模拟一些芯片的行为,然后与设计文件连接到一起仿真。

图2 语言测试程序对VHDL设计文件的协同仿真结构图

4 C语言对VHDL设计文件的协同仿真

4.1 构成框图

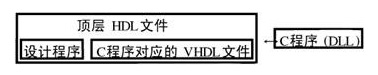

仿真文件的构成如图3所示,包括HDL文件和动态链接库(即c程序)。图中c程序对应的VHDL文件要负责声明对应的动态链接库文件名及初始化函数,另外还可以给出一些调用参数。动态链接中用到的输入输出信号也要在对应的VHDL文件中声明。

图3 仿真文件构成示意图

例如,假定有一个DLL文件名为sim.dll,对应的初始化函数为sim_init,有输入信号in1、in2,输出信号out1、out2,可以这样编写对应的VHDL文件

(sim.vhd):

library ieee;

use ieee.std_logic_1164.all;

entity sim is

port(

in1:in std_logic;

in2:in std logic;

out1:out std_logic;

out2:out std_logic;

);

end entity sire;

architecture dll of sim is

attribute foreign :string;

attribute foreign of dll :architecture is "sim_init

sim.dll”

begin

end;

仿真时,仿真器对顶层的HDL文件进行仿真,并根据各VHDL文件的动态链接库声明来调用、执行相应的动态链接库。

4.2 动态链接库的程序结构

利用modelsim仿真时,可根据VHDL文件的声明,调用DLL文件(如sim.dll)。在VHDL文件中已经给出了调用文件(sim.dll)和初始化函数名(如sim_init),modelsim根据这些信息,调用sim.dll中的sim_init函数,完成初始化工作。初始化包括:

①初始化全局变量;

②设置VHDL输入输出信号与c程序变量的对应关系;

③设置输出信号的一些初始状态(mti_ScheduleDriver);

④设置在仿真器重新仿真(restart)和仿真器退出仿真(quit)等情况下执行的一些函数(mti_AddRestartCB和mti_AddQuitCB等),如释放动态申请内存等;

⑤设置敏感表,给出在某些信号发生变化(如时钟上升沿等)时执行的函数。

⑥其它。

C程序的设计步骤如下:

(1)包含头文件,包括c程序常用的一些头文件和modelsim给出的外部语言接口头文件mti.h。Modelsim给出的外部接口函数说明、类型定义等都在mti.h中。

(2)定义自己的结构体,这一点主要是为了编程方便,例如输入输出信号对应的变量在各函数中基本上都会用到,可以把这些变量定义成一个结构,便于参数传递。

(3)编写初始化函数

初始化函数的定义为:

init_func(mtiReginoIdT region,char *param,

mtiInterfaceListT *generics,mtiInterfaceListT *ports)

各参数的意义可以参阅modelsim用户手册。

下面结合上面给出的初始化函数要完成的任务进行详细说明。

a.初始化全局变量(略)

b.设置VHDL输入输出信号与c程序变量的对应关系。这是通过调用mti_FindPort函数实现的。mti_FindPort函数定义为:

mfiSignalIdT mti_FindPort(mtiInterfaceListT *list,char *name);

例如,定义输入输出信号对应的结构ip:

PortStruct ip;

就可以用:

ip_in1=mti_FindPort(ports,"in1");

来实现输入信号in1与变量in1的对应关系。

对输出信号来说,它的目的是产生驱动。因此,这些变量(out1和out2)除了要找到对应的输出信号外,还要驱动这些信号。对信号的驱动可以通过调用mti_CreateDriver函数来实现。该函数的定义为:

mtiDriverIdT mti_CreateDriver(mtiSignalIdT sig);

由于这些变量一般只用于对外驱动,因此可以简单写成下面的形式:

ip.out1 = mti+ CreateDriver(mti_FindPort(ports,"out1"));

C.调用mti_ScheduleDriver函数,设置输出信号的初始状态。mti_ScheduleDriver函数的定义为:

void mti_ScheduIeDriver(mtiDriverIdT driver,long value,mtiDelayT delay,mtiDriverModeT mode);

其中,driver是输出信号对应的变量名,如ip.out1和ip.out2;value是要设置(驱动)的值,如高电平('1',对应value为3)、低电平('0',对应value为2)、高阻('z',对应value为4)、未赋值('U',对应value为0)等等;delay是从当前时间开始到把信号驱动成给定值(value)的等待时间,单位与仿真器当前使用的最小时间单位相同;mode为信号模式,有两个值可供选择:MTI_INERTIAL或者是MTI_TRANSPORT,分别对应于标准VHDL语言的INERTIAL和TRANSPORT。例如,设置信号out1的初始状态为低电平:

mti_ScheduleDriver(ip.out1,2,0,MTI_INERTIAL);

d.设置在仿真器重新仿真(运行命令restart)或退出仿真(运行命令quit-sim)等情况下调用的函数。这一部分主要是为了释放内存或者保存当前状态等。以restart为例,假设在程序中用malloc申请了存储空间buf,在仿真器"restart"时需要释放,就可以用以下的函数调用来注册:

mti_AddRestartCB(free,buf);

注册后,当仿真器运行命令restart时就会调用free(buf)。

其它一些函数可以参照modelsim的用户手册这里不再详述。

e.设置敏感表,给出在某些信号发生某些变化时(如时钟上升沿等)执行的函数。例如,在输入信号in1发生变化时,要执行函数in1_change(in1_change为用户定义好的函数),可以这样定义:

processed proc;

proc=mti_CreateProcess("P_in 1 change",in1_change,&ip);

mti_Sensitize(proc,ip.in1,MTI_EVENT);

也就是说,先创建进程,然后设置敏感表。当满足敏感表的条件时,仿真器就会执行该进程。

mti_CreateProcess函数的定义为:

mtiProcessldT mti_CreateProcess(char *name,mtiVoidFuncPtrT func,void * Param);其中,name是将要在仿真器窗口中显示的名称;func是要执行的函数;后面的param是要传给func的参数。mti_Sensitize的定义为:

void mti_Sensitize(mtiProcessIdT proc,mtiSignalIdT sig,mtiProcessTriggerT when);

其中,proc为调用mti_CreateProcess的返回值;sig为信号名,即VHDL文件的输入输出信号对应于C程序的变量;when可以取MTI_EVENT或者MTI_ACTIVE两种值。

4.3 C程序的编译

对Windows平台,采用的编译器是MicrosoftVisual C++,并用如下的命令进行编译:

cl -c -I app.c

link -dll -export: app.obj

modeltech.lib

上面的是modelsim的安装目录,是c程序的初始化函数名,如我们给出的sim.c的sim_init。编译之后就可以生成.dll文件。

仿真向量是用c语言还是用HDL直接产生,要视设计者的应用而定,选取最简单的方式。在大多数情况下,用c语言和HDL联合生成测试向量会更方便些。

5 结论

利用Moelsim的FLI功能,用c语言对所设计的模型进行功能验证,可以加大验证代码的覆盖率,减少验证代码的复杂度,加快验证的速度,缩短设计周期,可以更好的验证系统的通用性。另外,Modelsim的FLI功能使硬件描述语言(Verilog,VHDL)与c语言紧密结合在一起,为设计人员提供了更广阔的验证平台,更方便的验证方法。

温馨提示:明德扬2023推出了全新课程——

逻辑设计基本功修炼课,降低学习FPGA门槛的同时,增加了学习的趣味性

http://old.mdy-edu.com/chanpinzhongxin/peixunkecheng/2023/0215/1889.html

明德扬除了培训学习还有项目承接业务,擅长的项目主要包括的方向有以下几个方面:

1. MIPI视频拼接

2. SLVS-EC转MIPI接口(IMX472 IMX492)

3. PCIE采集系统

4. 图像项目

5. 高速多通道ADDA系统

6. 基于FPGA板卡研发

7. 多通道高灵敏电荷放大器

8. 射频前端

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

需要了解相关信息可以联系:吴老师18022857217(微信同步)