如果同学们的问题我们帖子里面没有的请第一时间联系我微信同步:18022857217吴老师,我们对新问题进行补充!

明德扬最近做了抖音系列短视频,感兴趣可以关注明德扬抖音号:FPGA技巧分享(87481069842)至简书籍短视频(74803215644)

内容不断更新!点赞+关注,学习不迷路!

1.《FPGA至简原理与应用》案例

1.1 FIR波形器 案例 相关编号:

【问题1.1.1】请问FIR滤波器中为什么要截断?MSB为什么要截断3位,LSB要截断19位?

答:在数字信号中,由于数据的位宽是有限的,例如int类型,其位宽是32位的。当计算结果超过位宽时,就必须做截断处理。截断时根据需要可保留高位截掉低位,这相当于整体除以1个数。

本案例中,我们数据的位宽是8位的,只能保留0~255这些数值,所以最终结果要在0~255范围之内。至于截断多少位,可以看这个帖子中的问题2:http://old.mdy-edu.com/wentijieda/20210410/1267.html

2. AD和DA案例

2.1 案例编号:000400000001 简易示波器

【问题2.1.1】 下载开发板后,无波形显示

答:可能的原因有如下,请逐个确认排除:

1. SMA线注意是要公头,请与开发板核对一下。

2. 信号发生器没有产生波形,可以将其接到示波器观察,确认是有波形输出的。

3. 阈值电平设置太高,没有达到触发的水线,要注意调节阈值,调节方法:MP801最右边的按键。

4. VGA线未连接。这个要看显示器,一般上电后,会显示背景图的。

5. 注意,设置完阈值后,一定要按按键s1 !!!只有按了S1,才能正常启动。

6,当显示的波形过于靠上或者靠下,以至于显示不完整的时候,请调节信号发生器输出波形的偏置。

7. 如果还有问题,请与我们客服联系,要求技术人员介入。

【问题2.1.2】显示出来波形在屏幕的最下面,而且只显示一部分。

答:调整信号发生器输入进来信号的偏置。

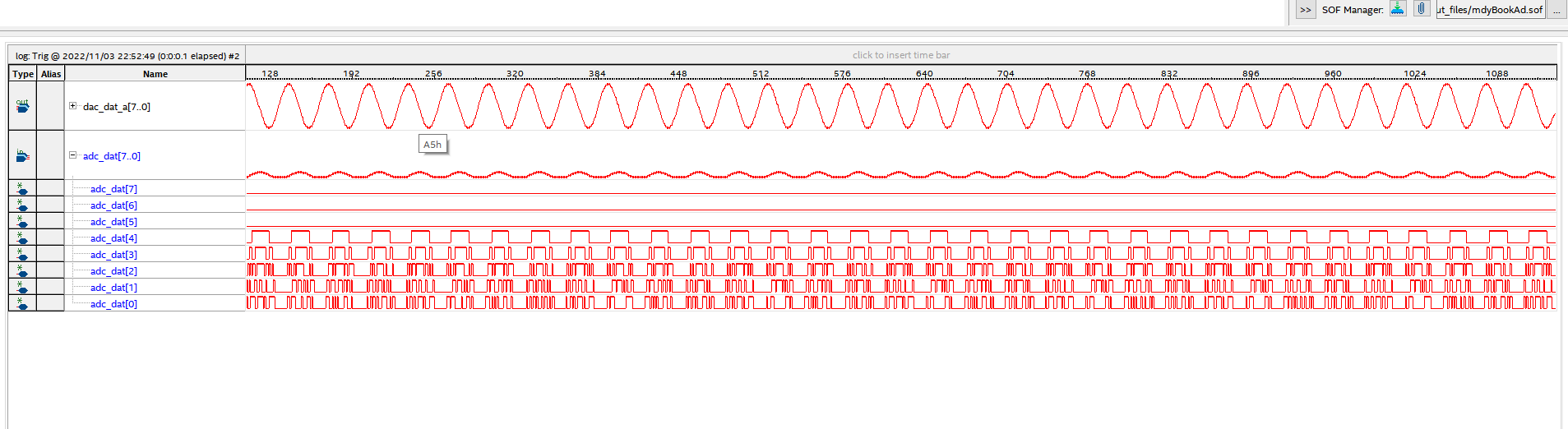

【问题2.1.3】ADC采集的数据一直很小,好像没采集到,如下图。

答:提供如下几个思路,请逐个确认。

1. 确保本案例中的SMA线连接正确,特别注意要三个SMA头,要选正确的连接。

2. 查看SMA线,MP801板上的SMA是母头,所以SMA线上应该是公头。

3. 换条SMA线看看,看不是线出问题了。

4. MP801的DAC输出电压是比较低的,经过环回后,AD采集的值比较小,这是正常的,应该能看出正弦波出来,如果看不到就是有问题。

5. 使用信号发生器产生激励,单独测试AD。6. dac_mode要设置为1。(注意,原工程有错误,新工程已经补充了)

7. 以上问题还没解决,可反馈给老师。

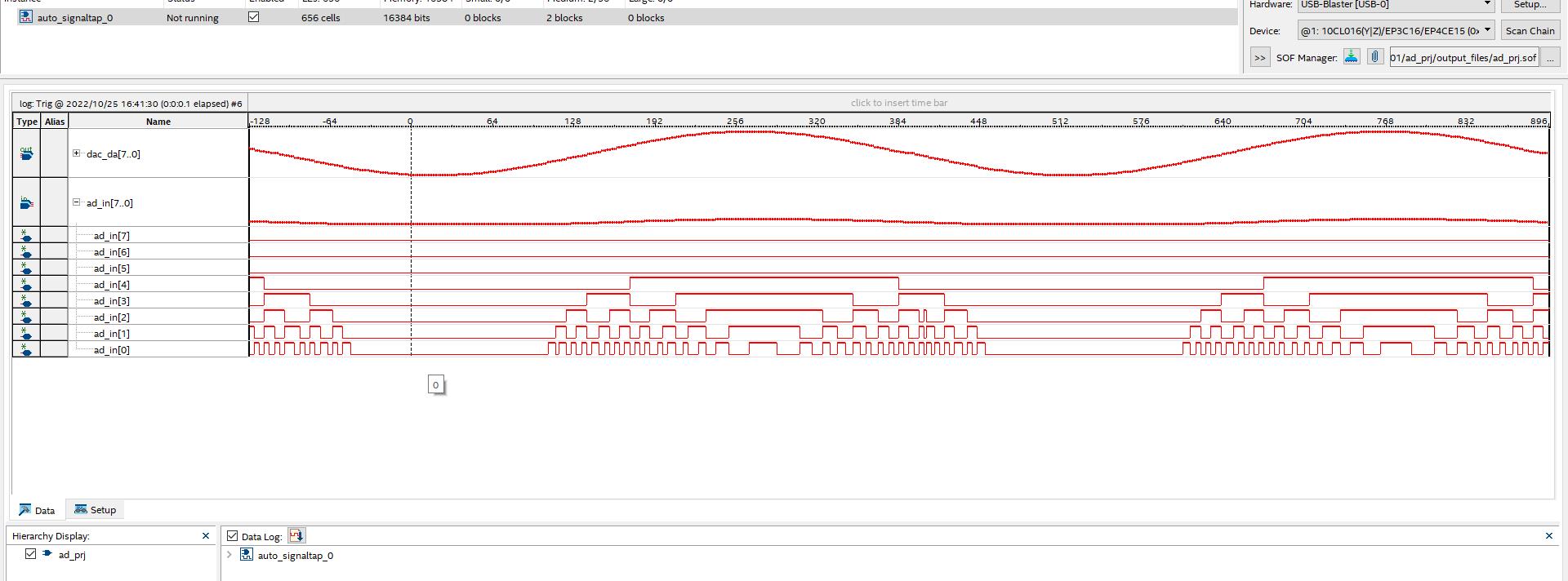

【问题2.1.4】AD采集案例现在就是仿真的时候不知道为什么那三位就是为0,上面波形出去的,下面波形采集刚出去的,采集是8位的,可以高三位一直为0,正常应该是有信号才对?

【问题2.1.5】请问项目就是那样的,然后第6条我之前改过了

我按照我这边的信号情况调了下管脚编号,现在这样了,目前的管脚分配是和文档里给的不一样的,另外不管怎调,总有三个管脚为0,就没变化

会不会是硬件问题?那个第6条的dac_mode呀,那个不改不行,那算是信号发生的控制位,那个不改的话,都没有信号发出的,然后我加了个那个,有信号发出了,接收到的最开始就是这样的

我调了下端口连接,现在是这样了,总有三个端口为0?

答:端口引脚不应该修改,否则结果错误。高3bits数据为0问题解答参考上述【问题1.1.4】

【问题2.1.6】至简最后一个案例工程AD采集,视频上面对于时钟分频采用的是锁相环,但是至简案例工程中代码不是用锁相环产生时钟

答:产生clk方式可以不一样

3. 边缘检测系列案例

3.1 边缘检测工程,相关案例编号:000500000002、000500000003、000500000004、000500000005、000500000006、000500000007、000500000008、000500000009

【问题3.1.1】点拨开发板,下载工程检测工程后,没有反应。

答:注意:下载后,需要按下矩阵键盘的按键0(即左上角第一个按键),才能显示!!!

【问题3.1.2】点拨开发板可以显示摄像头拍摄过来的图片吗?

答:由于点拨开发板的资源不足,所以无法显示摄像头的图片,如要显示,建议购买MP801开发板。

【问题3.1.3】PCLK和XCLK的异同

答:FPGA提供XCLK给摄像头,摄像头利用XCLK产生PCLK。所以PCLK来源于XCLK,所以XCLK是多少,PCLK就是多少。也就是说PCLK和XCLK频率大小一样,只是说可能不同相。

【问题3.1.4】是否不使用PLL,而是用PCLK来作为采集模块的时钟?

答:PCLK经过插件连到FPGA,由于连线问题,这可能会不稳定。为解决此问题,将PCLK连到PLL,产生一个同频同相的时钟,使用这个时钟作为采集模块的工作时钟。

这样,即使PCLK缺少或者不稳定,但产生的时钟也会保持稳定。

【问题3.1.5】摄像头寄存器配置模块中,配置的是04对应RGB,但是数据手册中RGB应该是01,这是为什么?

答: 这里的Bayer RAW本质上是RAW RGB格式,也是RGB格式。

RAW RGB:在摄像头里没有经过任何处理的数据。

RGB:在摄像头里经过了ISP等算法处理的数据。

如果想要最原始的数据,就使用RAW格式;如果要摄像头先美化一下,就使用RGB格式。想要哪种格式,取决于您的需求。

【问题3.1.7】现有vga的像素是[7:0] 需要将其移植到[9:0]的开发板中 是不是可以直接将 [9:0] <= {[7:0],[1:0]} 直接将低位补0?

答:像素变换的时候,要注意数据代表的含义。当是RGB格式并且VGA像素是8位,大概率是R323的格式。即data[7:5]是R,data[4:3]是G,data[2:0]是B。当要扩展位宽为10位的时候,就要考虑10位中,哪些位是表示R、G、B的,然后在相应的位置补0。假设分别是433来表示RGB,那么应该是这样拼接:{data[7:5],1'b0,data[4:3],1'b0,data[2:]}。上面是举例子,请按此种思想来变换位宽。【问题3.1.8】RGB565转成8位的灰度值,怎么转换成16位直接让vga输出?让vga输出这个8位的dout灰度值

答:三种颜色的低位补0即可。

【问题3.1.9】移位寄存器的IP核两个tap之间间隔的值可以任意设置吗,我看设置上只能设置2的次方的一些固定值,并且最大只能到256,

所以说边缘检测里说每个tap存640个数据是怎么达到的呢?

答:界面上下拉出来的是一些常用值,实际上是可以直接填数的,在界面上直接填上您需要的数即可。

4.中型综合案例

4.1 简易计算器,编号:000600000010

【问题4.1.1】在简易计算器的“工作状态选择模块”代码中,有一个状态机,但状态机的跳转条件没有定义,没有数据类型,可以直接用吗?

答:在VERILOG代码中,如果对信号没有定义,默认的为1位的wire型。按这个去使用即可。

5.串口案例

5.1串口相关案例,相关编号:000900000237,000900000238,

【问题5.1.1】在串口回环工程中,数据处理模块中ifdef XILINX的意思是什么?

答:他的下面是XILINX的ip核,当定义这个宏的时候,就会使用这个ip核,没有定义,则使用my_fifo这个ip核代码。

【问题5.1.2】打开串口调试助手的时候,提示没有发现此串口。如何解决?

答:1、可以在电脑设备管理器中的端口选项下,找到对应的串口号,然后串口调试助手选择相应的串口号即可。ps:若设备管理器中没有端口选项,在上方点击“查看”,然后选择“显示隐藏的设备”

2、如果设备管理器中显示的端口号,软件上没有,可以按照以下操作修改串口号:选中端口选项下面的串口号→右键单击选择属性→端口设置→高级,然后在最下面修改对应的端口号即可

3、https://jingyan.baidu.com/article/e52e36157a2dc740c70c514d.html

【问题5.1.3】串口环回工程输入数据之后点一下发送并不能收到,要点好多下发送他才能收到一些数据是什么原因?

【问题5.1.4】串口环回工程我想实现发一个收一个的功能,应该如何修改代码。

答:提供两种方法思路供,具体请自行实践。方法1思路: 保证串口接收模块和串口发送模块,不需要data_handle模块。串口接收模块的输出直接连到串口发送模块的输入。

方法2思路:打开data_hanle模块,将“60”这个数字改为1。

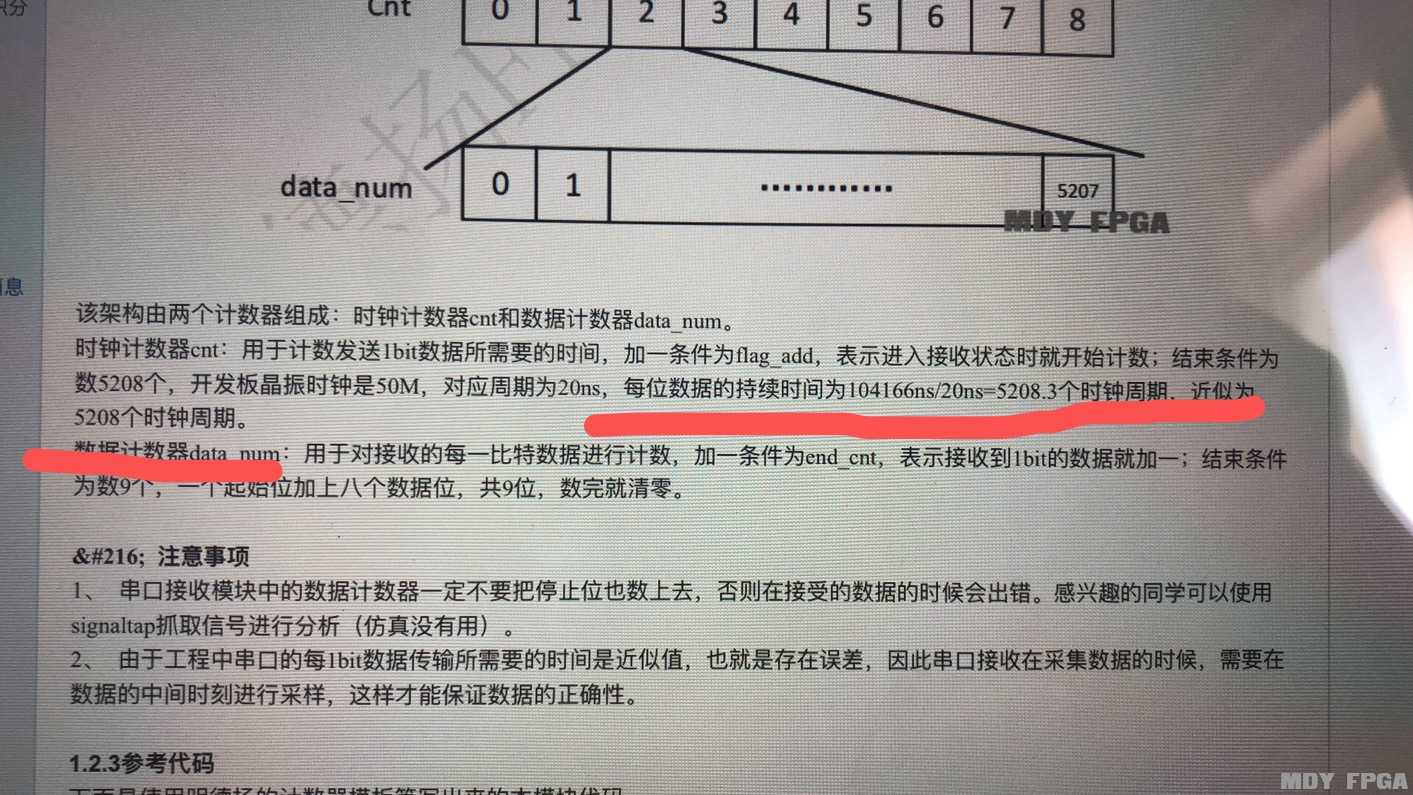

【问题5.1.5】在串口接收中,为什么要在数据的中间时刻进行采样而不是在开始和结尾?

答:由于我们通过计数器对数据的长度进行计数的时候是有误差的,在开始和结尾进行采样的话数据容易出错。详情请看下面的案例文章:【每周FPGA案例】至简设计系列_串口回环工程

http://fpgabbs.com/forum.php?mod ... 1074&fromuid=100110

【问题5.1.6】请问这个104166是怎么得来的?

答:波特率为9600,那么1秒时间传输的数据个数为9600,每个数据需要的传输时间为:1s/9600约等于0.000104166s,即104166ns。

【问题5.1.7】串口接收模块中,为什么计数器不数停止位,数了就错呢?

接收方向,不数停止位,那么接收完毕是在最后一个数据,或者停止位这个时刻上,然后会开始捕捉新的一段数据 的“开始位下降沿”,那么这个时候就正常了。

6.VGA案例

6.1 VGA相关案例,相关编号:

【问题6.1.1】VGA案例中,使用25M的频率,是怎么算出来的?

答:MDY默认的案例是640*480分辨率,加上前沿、后沿等,是800*525,60帧/秒。即每帧占用时间为:(1/60)秒,每个像素时间是:(1/60)/(800*525),结果约为40ns,即25M,这是每个像素的时间。

7.其他接口案例

7.1 超声波测距系统,编号:000700000011

【问题7.1.1】非MP603、MP801的管脚配置问题。

答:超声波模块有4根管脚,分别是VCC、GND、echo和trig。如果您使用非MP603和非MP801开发板(案例中的开发板),

则记得电流和GND要接正确,而echo和trig可以插在任意通用IO口上,然后FPGA管脚要配置正确,这样就可以了。

【问题7.1.2】MP603点拨开发板中,绿色线连到哪里?图上不清晰

答:连到P1座子的1位置上,即电源3.3V位置上。

【问题7.1.3】 数据管上的显示的距离不稳定,数字会跳变。

答:超声波的原理是发出超声波,遇到障碍物后返回,从而得到距离。如果数字不稳定,可能是障碍物硬度不够,请换一个厚点的障碍物测试。

【问题7.1.4】超声测距案例中,h_cnt的位宽如何确定?

答:h_cnt用于计算flag高电平时间,即回响电平时间。由于该值不确定,可以计数器位宽可以设为一个“最大可能时间”,例如可以设为1秒。根据1秒再换算成h_cnt的位宽。

8.DDS案例

【问题8.1.1】DDS设计案例中,实现的是一个时钟输出一个数据点。为了产生更高的信号,是否可以一个时钟输出多个点。

答:假设一个数据由8位组成,一个时钟输出1个数据,是输出8位。为了提高频率,可以一个时钟输出多个数据,例如2个数据,则输出数据由16位组成,其中高8位是第1个数据,低8位是第2个数据。

但注意,这个方式的前提是,DA芯片支持多个数据输入。因为最终是由DA接收这些数据并转换成模拟信号的。