本文为明德扬原创文章,转载请注明出处!

这里分享的是基于altera的A10 DDR3的IP核配置具体操作。关于DDR IP核的接口配置,参考的是avalon-mm协议,想要了解更多关于avalon-mm协议,大家可以查看的相关资料。

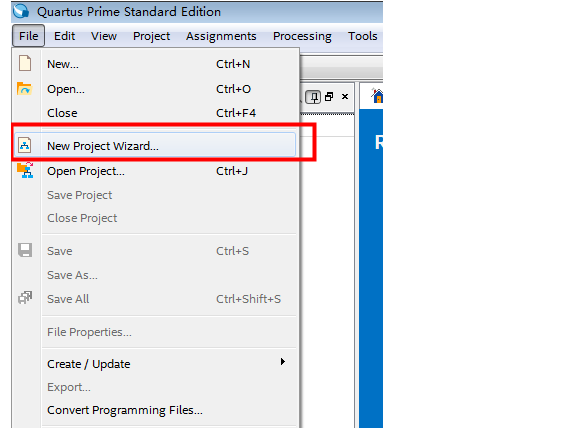

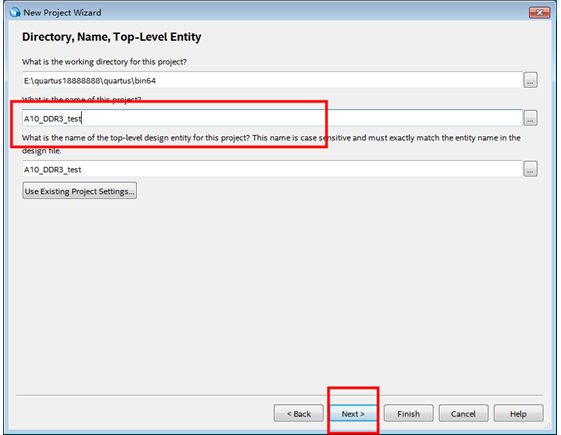

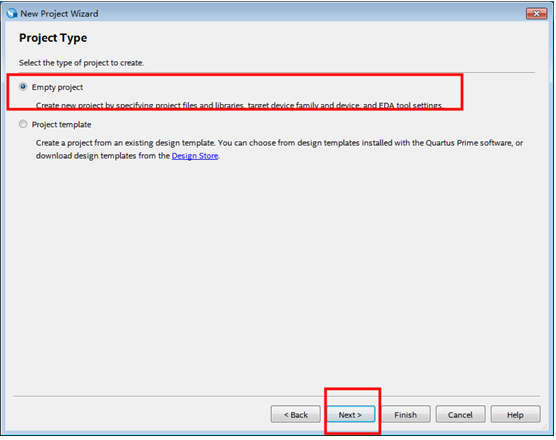

一、用quartus 18版本新建一个工程,可命名为“A10_ddr3_test”(如下图所示)。

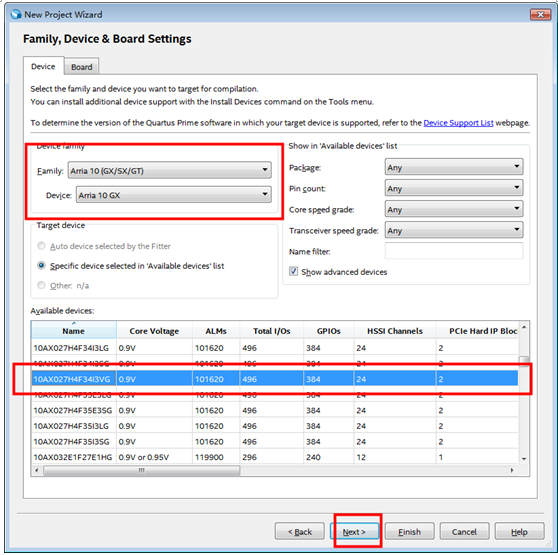

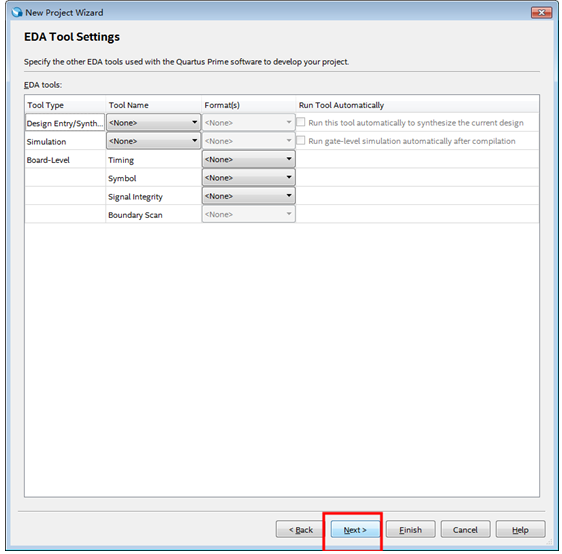

这里我们选择的芯片是:10AX027H4F34I3VG,大家可以根据自己的需要选择相应芯片,然后点击“Next”。(如下图①所示)

图①

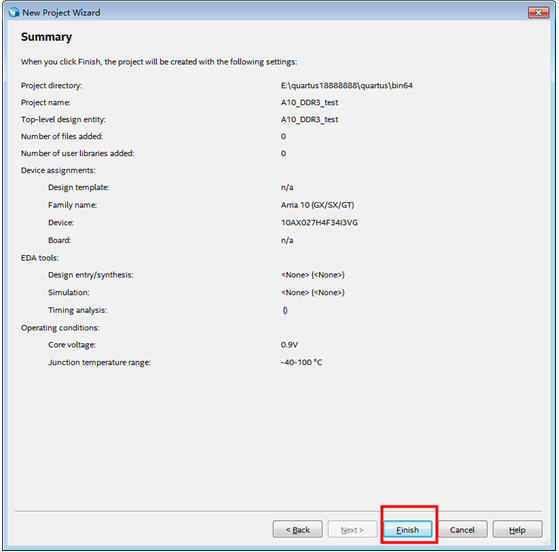

检查看看生成的工程概况是否正确,没问题就点击“Finish”结束工程的建立(如下图所示)。

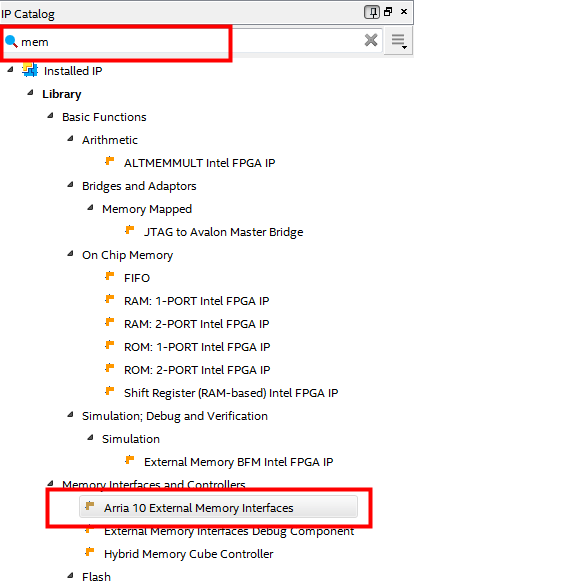

二、在quartus的右边“IP Catalog”界面搜索栏里输入“mem”,快速搜索“Arria 10 External Memory Interfaces”,双击进入IP核的配置(如下图所示)。

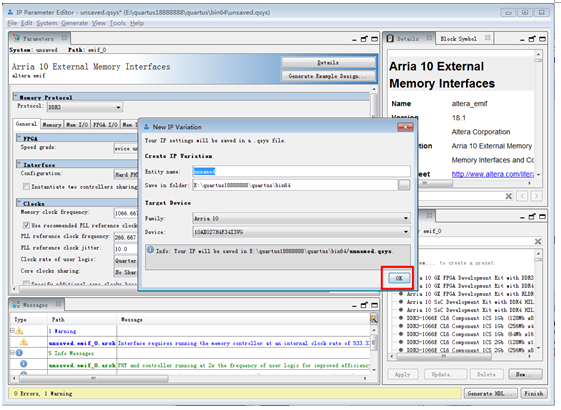

三、弹出的IP核配置界面如下,确定芯片型号没问题后点击“OK”

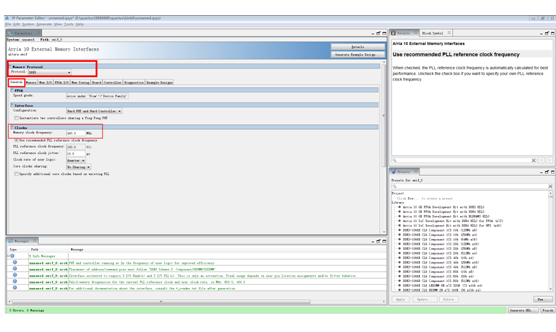

四、在配置界面,“Memory Protocol”à 选择“DDR3”;在“General”页面 à “Clocks” à “Memory clock frequency”配置DDR的速率为“400.0”MHz(如下图所示)。

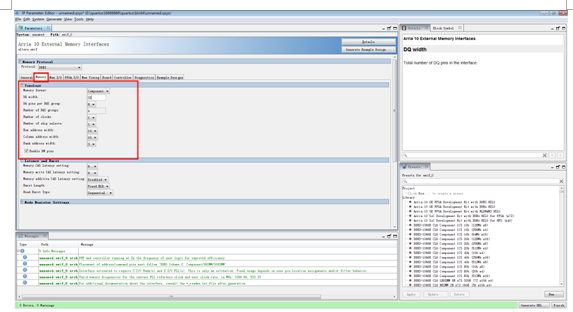

五、在页面“Memory”à “Topology”部分,根据硬件Datasheet手册来配置。

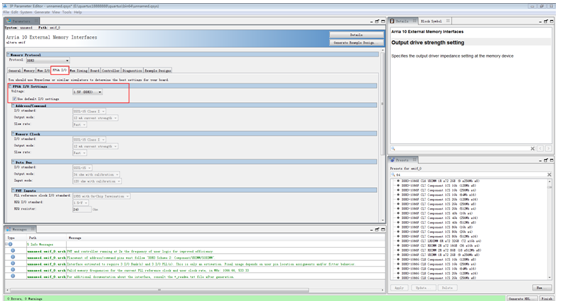

六、在页面“FPGA I/O”à “FPGA I/O Settings”,同样都是根据硬件Datasheet手册来设置,这里选择“1.5V(DDR3)”(如下图所示)。

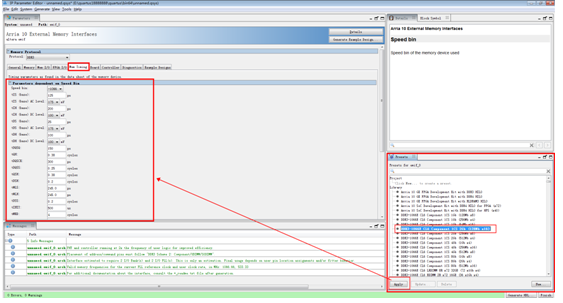

七、在页面“Men Timing”à “Parameters dependent on Speed Bin”部分也是根据硬件手册来设置,但比较繁琐,此时我们可以在右下角“Presets”界面找到相应的DDR3 IP核,然后点击“Apply”来自动配置参数,这里我们选择的IP核是“DDR3-1066E CL6 Component 1CS 2Gb (128Mb x16)”(如下图所示)。

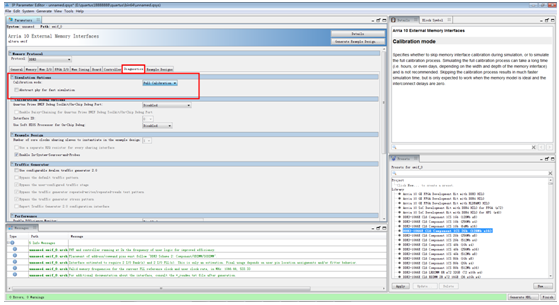

八、在页面“Diagnostics”à “Simulation Options”à“Calibration mode”,选择“Full Calibration”(如下图所示)。

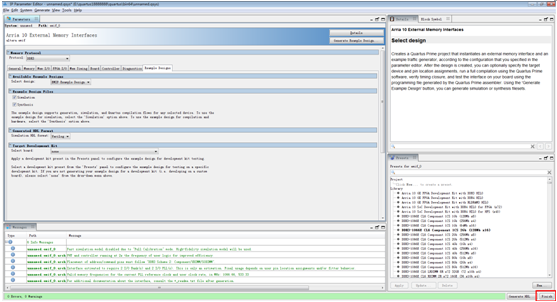

九、点击配置界面右下角“Finish”结束IP核的配置,之后弹出的界面点击“Close”(如下图所示)。

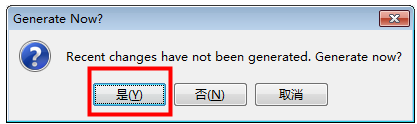

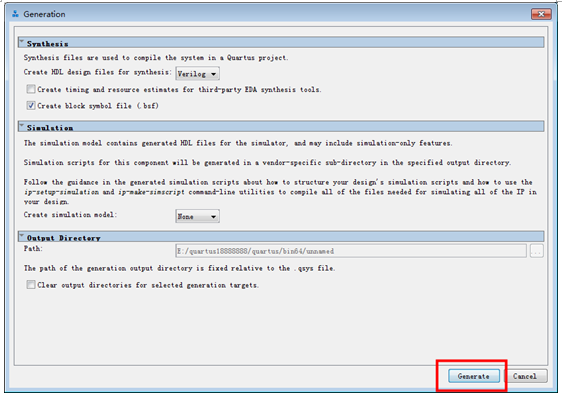

十、点击“是”,再点击“Generate” 确认生成IP核(如下图所示)。

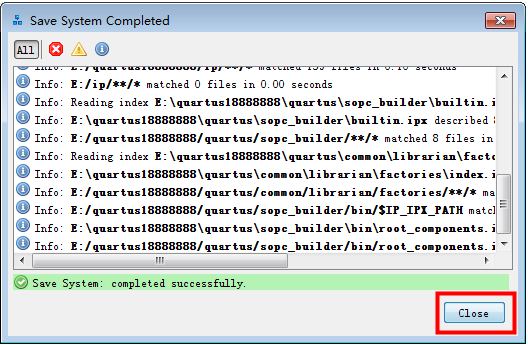

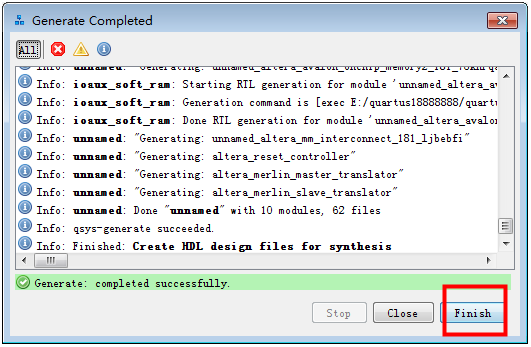

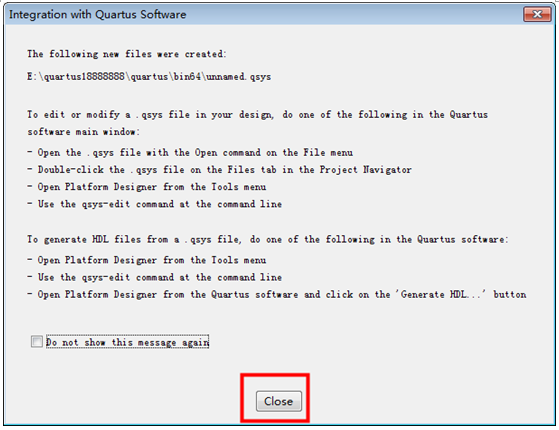

十一、 生成IP核结束,点击“Finish”,再点击“close”。

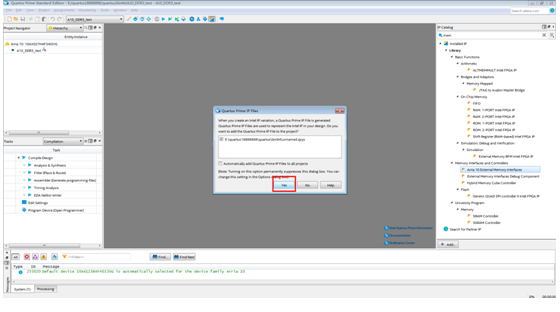

十二、 点击“Yes”,确认加入工程(如下图所示)。

以上就是基于altera的IP核配置的具体操作。如有不明白的地方可以加我的QQ:1479512800,共同讨论,期待与大家一起探讨进步!