本文的文档编号:002700000026

需要看对应的视频,请点击视频编号:000600000419

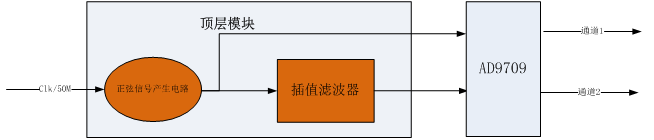

1、本文档讲述FPGA产生两路正弦波数据,一路直接由DA输出,一路经过CIC处理之后输出,然后传到示波器进行观察,从而了解CIC滤波器的效果

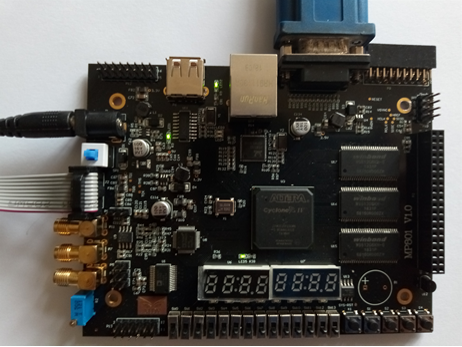

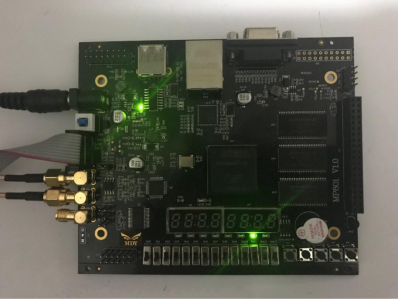

2、801开发板使用

1项目背景

1.1多采样率数字滤波器

多采样率就是有多个采样率的意思。前面所说的FIR,IIR滤波器都是只有一个采样频率,是固定不变的采样率,然而有些情况下需要不同采样频率下的信号。 按照传统的速率转换理论,我们要实现采样速率的转换,可以这样做,假如有一个有用的正弦波模拟信号,AD采样速率是f1,现在我需要用到的是采样频率是f2的信号,传统做法是将这个经过f1采样后的信号进行DA转换,再将转换后的模拟信号进行以f2采样频率的抽样,得到采样率为f2的数字信号,至此完成采样频率的转换 但是这样的做法不仅麻烦,而且处理不好的话会使信号受到损伤,所以这种思想就被淘汰了,现在我们用到的采样率转换的方法就是抽取与内插的思想。

1.2抽取

先来总体来解释一下抽取的含义:前面不是说,一个有用的正弦波模拟信号经采样频率为f1的抽样信号抽样后得到了数字信号,很明显这个数字信号序列是在f1频率下得到的,现在,假如我隔几个点抽取一个信号,比如就是5吧,我隔5个点抽取一个信号,是不是就是相当于我采用了1/5倍f1的采样频率对模拟信号进行采样了?所以,抽取的过程就是降低抽样率的过程,但是我们知道,这是在时域的抽样,时域的抽样等于信号在频域波形的周期延拓,周期就是采样频率,所以,为了避免在频域发生频谱混叠,抽样定理也是我们要考虑的因素。

下面来具体来介绍

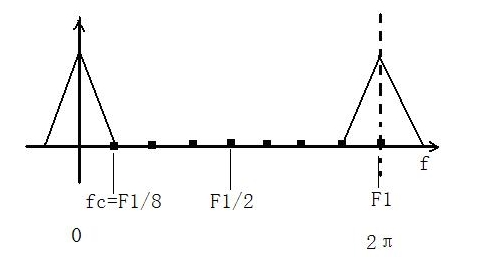

图561

如上图所示,假如上面就是某一有用信号经采样频率f1抽样得到的频谱,假设这时候的采样频率为8Khz,可以通过数格子得到,从0到F1处有8个空格,每个空格代表1Khz,有些朋友可能会问,这不是在数字频域吗,单位不是π吗,哪来的hz?是的,这里是数字频域,采样频率F1处对应的是2π,这里只是为了好解释,我们用模拟频率来对应数字频率。

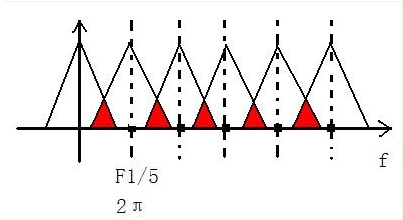

图562

上面是采样频率为8K的数字信号频域图,现在我要对这个数字信号进行时域抽取,从而来降低信号的采样率,我们知道,一旦我们对数字信号进行时域抽取,那么采样率下降,而采样率就是数字信号频域的波形周期,那么也就是周期下降,所以,我们对信号进行抽取要有个度,要在满足抽样定理的条件下对信号进行抽取,否则就会发生频谱混叠。

上图就是对信号进行了1/5倍的F1采样频率抽取,可见,由于发生了频谱混叠现象,因为1/5倍的F1是1600hz,而信号的频带是1000hz,不满足抽样定理,导致发生了频谱混叠,所以,为了避免发生这种情况,除了要满足抽样定理之外,即抽样倍数不能太高,我们还需要把信号的频带设置在F1/2以下,才能确保信号不发生频谱混叠,因此,我们需要在抽取之前加一个低通滤波器,书上叫做抗混叠低通滤波器,用来限制信号的频带,然后再进行抽取,这样的话我们来算一下

低通滤波器的截止频率就是1/2倍的经抽取后的采样速率,即fc = 1/2 *(F1/M) ,M是抽取倍数。而1/2*F1对应的数域频率是π,因此我们得出,

抗混叠低通滤波器的截止频率是π/M

1.3内插

抽取的过程是降低采样率的过程,那么插值的过程当然就是提高采样率的过程。大体的思路可以这么理解,我们将经f1抽样下得到的数字信号的每两个点之间进行插值,插入的值是0,插值之后,信号在单位时间内的采样点数增多,当然也就是采样速率的提升,采样速率提升后我们知道,那么信号的频谱的周期就会增加

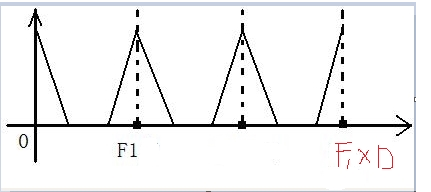

图563

需要注意的一点就是,插值前后,我们只是在时域信号中间插入了D-1个零值,仅仅是改变了采样率,并没有改变信号的信息,因此,在频域,信号频谱的形状是不会改变的,改变的仅仅是周期,如上图,F1是插值之前信号的周期,插值之后,信号频谱的形状不变,周期成了F1*D,D是插值倍数。如果我们直接用F1*D倍的采样率采信号,得到的频谱会发现,就不会有中间两个波形,因此,这两个波形是多余的,书上叫做是镜像频谱。既然是多余的,我们就可以将它用一个低通滤波器滤掉,这样的低通滤波器,就叫做镜像低通滤波器。这样我们来计算一下镜像低通滤波器的截止频率

图564

根据上面这张图我们可以求出镜像低通滤波器的截止频率,可以看到,fc = 1/2 *F1,这里我们假设,内插之后的采样频率为F2 =F1*D,那么,fc =1/2*(F2/D),而1/2*F2对应的是π,注意,这里是1/2*F2对应π,不是1/2*F1了,因为这已经是插值之后采样率增加之后的频谱了,所以我们得出:

镜像低通滤波器的截止频率为:π/D

2设计目标

本次案例将使用到采样率大于100M的双通道的示波器。将示波器的两个通道,分别与FPGA的DA通道1和DA通道2相连,观察两路DA的输出。其连接示意如下图所示。

图565

本案例是FPGA内部产生正弦信号,这个正弦信号一路输出给DA通道A,另一路经过插值滤波器后,输出给DA通道B。

图566

正弦信号产生电路产生频率为62.5KHz的正弦信号,该正弦信号由8个点组成。

插值滤波器是4倍的插值,也就是说进来是8个点的正弦波,输出将是32个的正弦波。

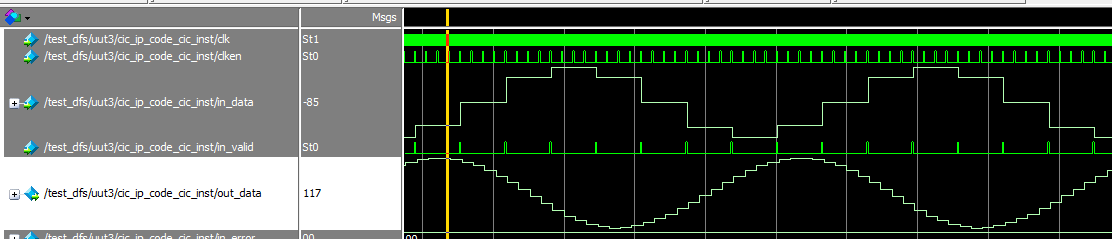

仿真效果,上面的波形为插值前,下面的为插值后可以明显看出下面的波形更为圆滑。

图567

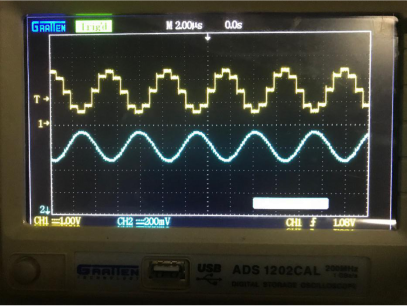

下面是示波器的显示效果

图568

上面黄色是通道1输出的信号,下面蓝色是通道2的输出信号。

上板效果图如下图所示。

3设计实现

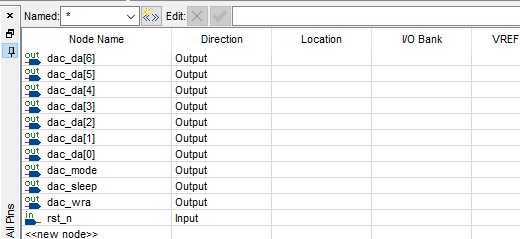

3.1顶层信号

新建目录:D:mdy_bookcic_prj。在该目录中,新建一个名为cic_prj.v的文件,并用GVIM打开,开始编写代码。

我们要实现的功能,概括起来就是FPGA产生控制AD9709,让其中的通道A未滤波的正弦信号,让通道B输出滤波后的正弦信号。为了控制AD9709的工作模式,就要控制AD9709的MODE、SLEEP管脚;为了控制通道A,就需要控制AD9729的CLK1、WRT1、DB7~0P1管脚;为了控制通道B,就需要控制AD9729的CLK2、WRT2、DB7~0P2管脚。根据设计目标的要求,整个工程需要以下信号:

1.使用clk连接到晶振,表示50M时钟的输入。

2.使用rst_n连接到按键,表示复位信号。

3.使用dac_mode信号连接到AD9709的MODE管脚,用来控制其工作模式。

4.使用dac_sleep信号连接到AD9709的SLEEP管脚,用来控制其睡眠模式。

5.使用dac_clka信号连接到AD9709的CLK1管脚,用来控制通道A的时钟。

6.使用dac_wra信号连接到AD9709的WRT1管脚,用来控制通道A的写使能。

7.使用8位信号dac_da连接到AD9709的DB7~0P1管脚,用来控制通道A的写数据。

8.使用dac_clkb号连接到AD9709的CLK2脚,用来控制通道B时钟。

9.使用dac_wrb号连接到AD9709的WRT2脚,用来控制通道B使能。

10.使用8位信号dac_db接到AD9709的DB7~0P2脚,用来控制通道B写数据。

综上所述,我们这个工程需要10个信号,时钟clk,复位rst_n,dac_mode、dac_sleep、dac_clka、dac_wra、dac_da、dac_clkb、dac_wrb和dac_db信号,其中dac_da和dac_db是8位信号,其他都是1位信号。下面表格表示了硬件电路图的连接关系。

|

器件 |

AD9709管脚 |

原理图信号 |

FPGA管脚 |

FPGA工程信号 |

|

U8 |

MODE |

DAC_MODE |

Y4 |

dac_mode |

|

SLEEP |

DAC_SLEEP |

H2 |

dac_sleep |

|

|

CLK1 |

DA_CLKA |

R2 |

dac_clka |

|

|

WRT1 |

DA_WRA |

U1 |

dac_wra |

|

|

DB7P1 |

DAC_DA7 |

AA1 |

dac_da[7] |

|

|

DB6P1 |

DAC_DA6 |

Y2 |

dac_da[6] |

|

|

DB5P1 |

DAC_DA5 |

Y1 |

dac_da[5] |

|

|

DB4P1 |

DAC_DA4 |

W2 |

dac_da[4] |

|

|

DB3P1 |

DAC_DA3 |

W1 |

dac_da[3] |

|

|

DB2P1 |

DAC_DA2 |

V2 |

dac_da[2] |

|

|

DB1P1 |

DAC_DA1 |

V1 |

dac_da[1] |

|

|

DB0P1 |

DAC_DA0 |

U2 |

dac_da[0] |

|

|

CLK2 |

DA_CLKB |

R1 |

dac_clkb |

|

|

WRT2 |

DA_WRB |

P2 |

dac_wrb |

|

|

DB7P2 |

DAC_DB7 |

P1 |

dac_db[7] |

|

|

DB6P2 |

DAC_DB6 |

N2 |

dac_db[6] |

|

|

DB5P2 |

DAC_DB5 |

N1 |

dac_db[5] |

|

|

DB4P2 |

DAC_DB4 |

M2 |

dac_db[4] |

|

|

DB3P2 |

DAC_DB3 |

M1 |

dac_db[3] |

|

|

DB2P2 |

DAC_DB2 |

J1 |

dac_db[2] |

|

|

DB1P2 |

DAC_DB1 |

J2 |

dac_db[1] |

|

|

DB0P2 |

DAC_DB0 |

H1 |

dac_db[0] |

|

|

X1 |

|

SYS_CLK |

G1 |

clk |

|

K1 |

|

SYS_RST |

AB12 |

rst_n |

将module的名称定义为cic_prj,代码如下:

|

1 2 3 4 5 6 7 8 9 |

module cic_prj( clk , rst_n , dac_mode , dac_sleep , dac_clka , dac_da , dac_wra , dac_clkb , dac_db , dac_wrb ); |

其中clk、rst_n是1位的输入信号,dac_da和dac_db是8位的输出信号,dac_mode,dac_clka,dac_wra,dac_sleep,dac_clkb,dac_wrb是一位输出信号。

|

1 2 3 4 5 6 7 |

input clk ; input rst_n ; output dac_mode ; output dac_clka ; output [ 8-1:0] dac_da ; output dac_wra ; output dac_sleep ; output dac_clkb ; output [ 8-1:0] dac_db ; output dac_wrb ;

|

3.2正弦信号设计

假设产生的正弦信号命名为sin_data信号。sin_data一共有8个值,是从一个正弦信号中,按(2*pi/8)的间隔采样到的,可列出下表。

|

采样点i |

sin_data (16进制) |

采样点i |

sin_data (16进制) |

采样点i |

sin_data (16进制) |

采样点i |

sin_data (16进制) |

|

0 |

7F |

2 |

FE |

4 |

7D |

6 |

1 |

|

1 |

DA |

3 |

D8 |

5 |

23 |

7 |

2A |

很自然地定义一个7位的选择信号addr。我们只要控制好addr,就能方便得到sin_data。因此可以写出下面代码。

|

1 2 3 4 5 6 7 8 9 |

always @(*)begin case(addr) 0: sin_data = 8'h7F; 1: sin_data = 8'hDA; 2: sin_data = 8'hFE; 3: sin_data = 8'HD8; 4: sin_data = 8'h7D; 5: sin_data = 8'h23; 6: sin_data = 8'h1; 7: sin_data = 8'h2A; endcase end |

接下来是设计信号addr。

addr是用来控制选择数据的地址,通过控制addr的增加值,就能产生所需要的正弦波。

本案例要求产生62.5KHz的正弦信号。该正弦信号的周期是16000ns。本工程的工作时钟是20ns,也就是16000/20 = 800个时钟输出一个正弦信号,也就是800个时钟将上表的8个值输出一遍,即每100个时钟输出addr加1。

每100个时钟输出一个值,那意味着我们需要一个计数器cnt0,该计数器用来对这100进行计数。计数器的加1条件是“1”,结束条件是“数到100个”。因此可写出cnt0的代码。

|

1 2 3 |

always @(posedge clk or negedge rst_n) begin if (rst_n==0) begin cnt0 <= 0; end else if(add_cnt0) begin if(end_cnt0) cnt0 <= 0; else cnt0 <= cnt0+1 ; end end assign add_cnt0 = 1; assign end_cnt0 = add_cnt0 && cnt0 == 100 -1 ; |

每100个时钟后,addr就加1。说明这个addr也是一个计数器,该计数器的加1条件是“数到100个时钟”,即end_cnt0,结束条件是“数到8个”。

|

1 |

always @(posedge clk or negedge rst_n) begin if (rst_n==0) begin addr <= 0; end else if(add_addr) begin if(end_addr) addr <= 0; else addr <= addr+1 ; end endassign add_addr = end_cnt0; assign end_addr = add_addr && addr == 8 -1 ; |

3.3CIC滤波器设计

3.3.1新建FPGA工程

图569

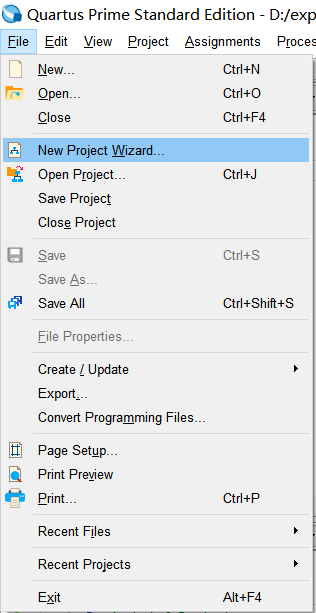

1.打开quartus,点击File在File菜单中选择New Project Wizard....。

图570

2.弹出Introduction界面选择Next。

图571

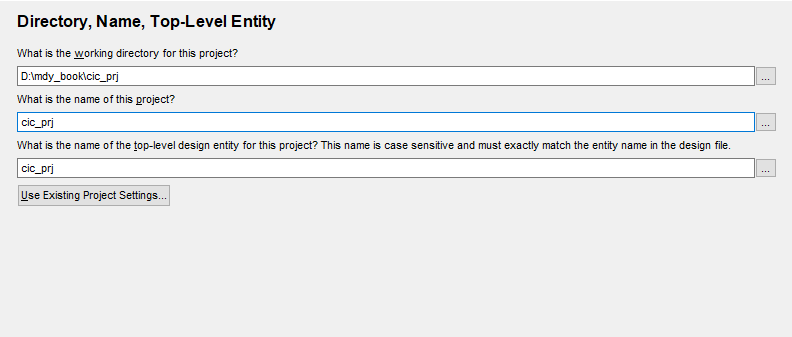

3.设置工程目录,工程名,顶层模块名

工程目录设置为:D:mdy_bookcic_prj

工程名:cic_prj

顶层模块名:cic_prj

填写完毕后,点击next之后进入下一界面。

图572

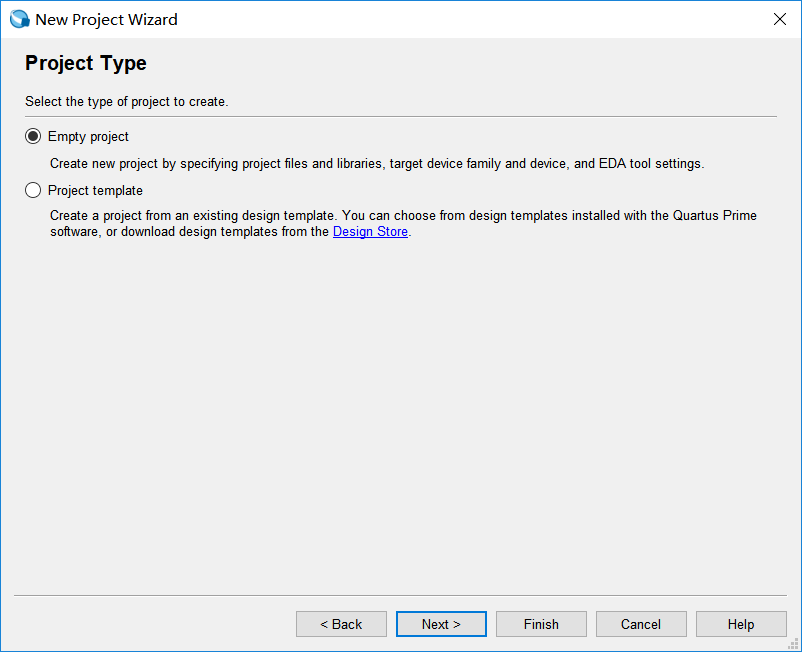

4.工程类型界面,Project Type选择Empty project,选择空白工程。点Next进入下一个界面。

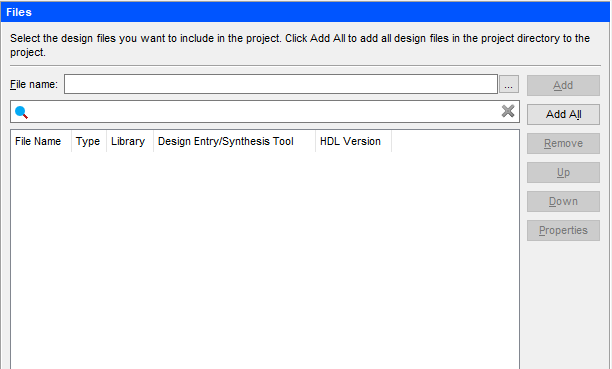

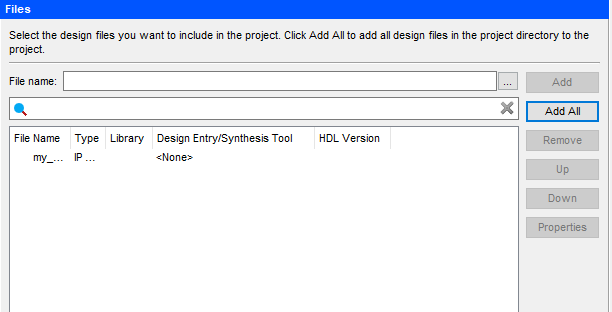

图573

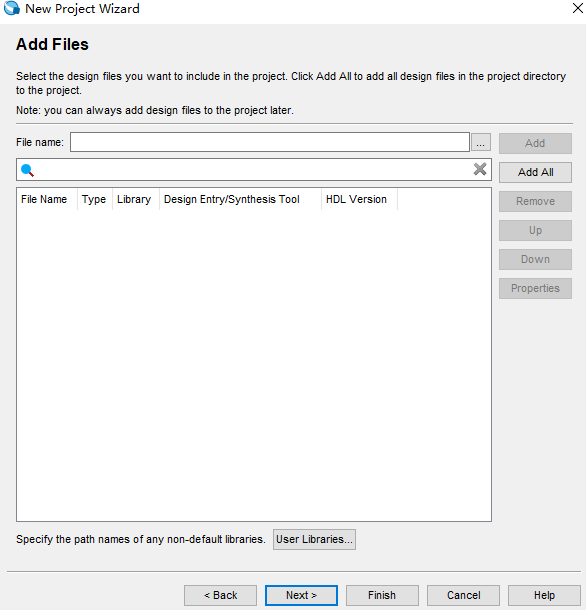

5.在文件添加界面,不选择任何文件。点击Next,进入下一个界面。

图574

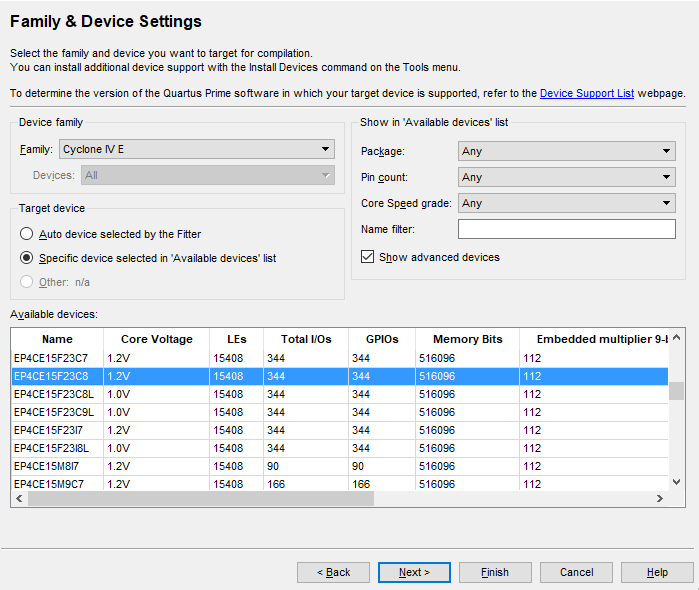

6.器件选择界面。在Device family这一项之中选择Cyclone IV E;在下部的Available device选择EP4CE6F23C8。完成后直接点击Finish。

3.3.2FPGA生成CIC IP核

图575

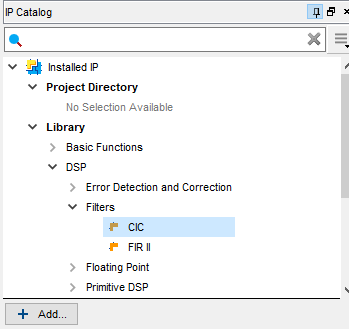

建立工程后,在quartus中IP catalog这一界面中选择DSP下一目录中选择Filter再选择CIC。

图576

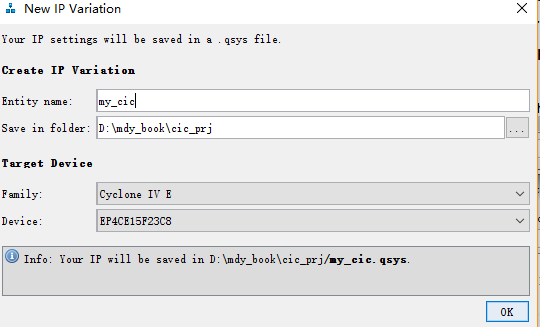

点击后进入此界面给新生成的fir滤波器ip核选择如下路径:D:mdy_bookcic_prj,entity name填写:my_cic。点击OK后,进入FIR滤波器设置界面。

图577

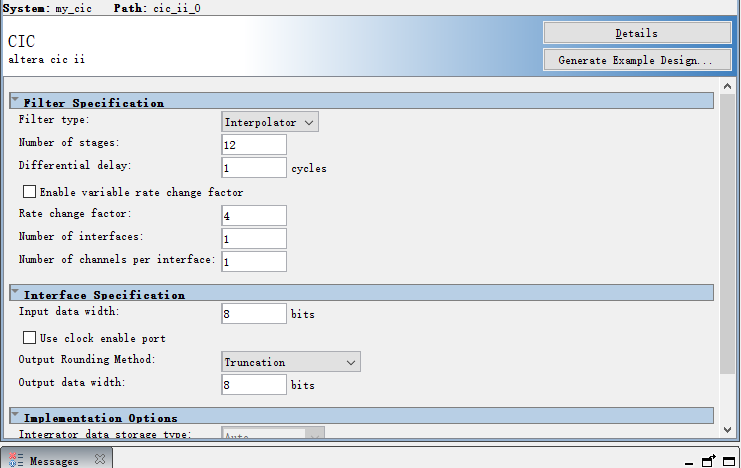

按如下设置:

Filter Type:要选择Interpolator,表示是插值滤波器。

Rate change factor:填上4,表示是4倍插值。

output Rounding Method:选择Truncation,表示输出的结果要截断。

Output data width:选择8。表示输出结果要截断为8位。

其他选项默认,点击窗口右下角的Generate Hdl,会弹出下面的窗口。

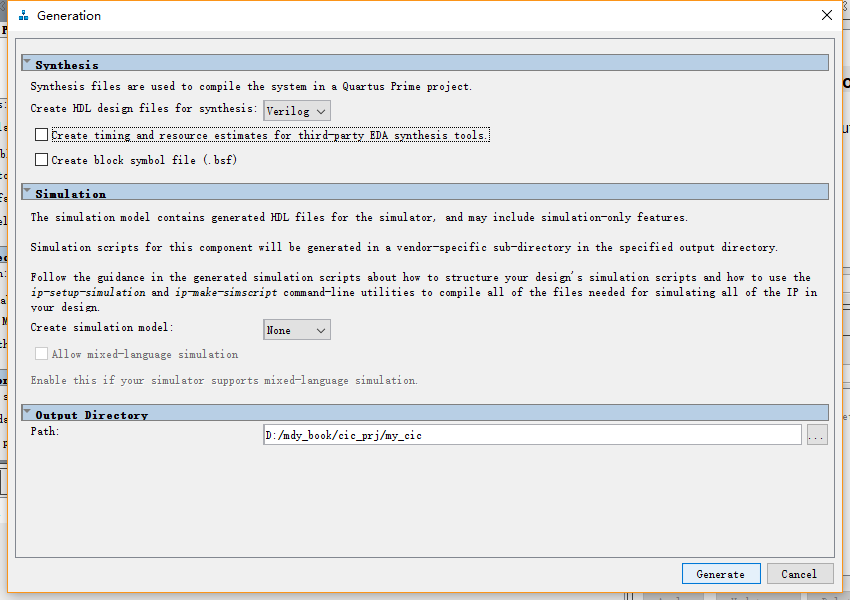

图578

注意选择文件是Verilog文件,其他都不用勾选。点击Generate,就会生成y_cic的verilog文件。

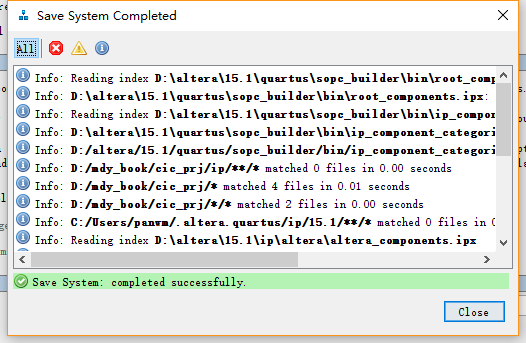

图579

出现上面的提示,就是生成成功了。

点Finish关闭CIC滤波器生成窗口。

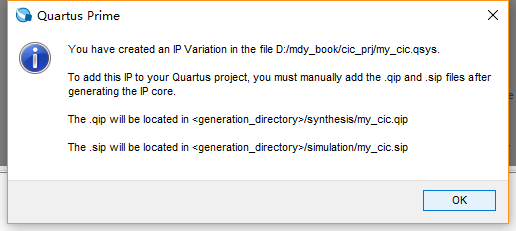

图580

如果出现上面的提示,就是表示要手动将刚才生成的IP核加到本工程。

图581

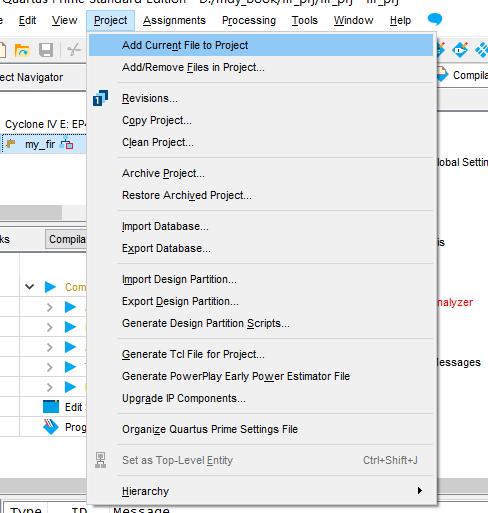

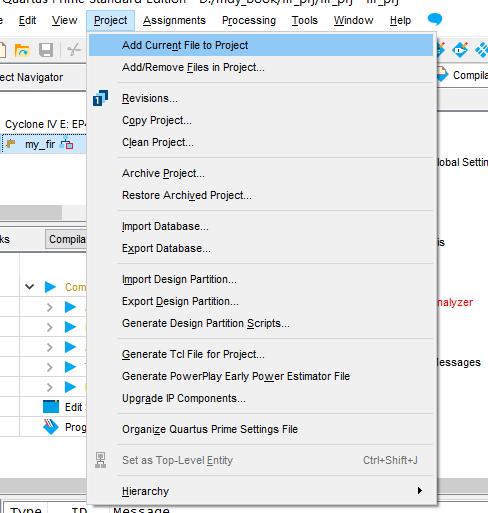

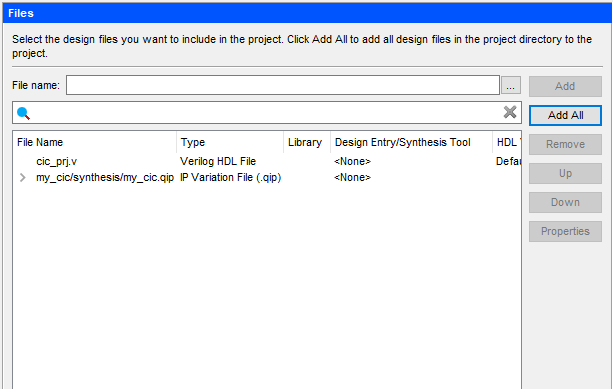

在Project菜单中选择Add/Remove File to Project,弹出文件窗口。

图582

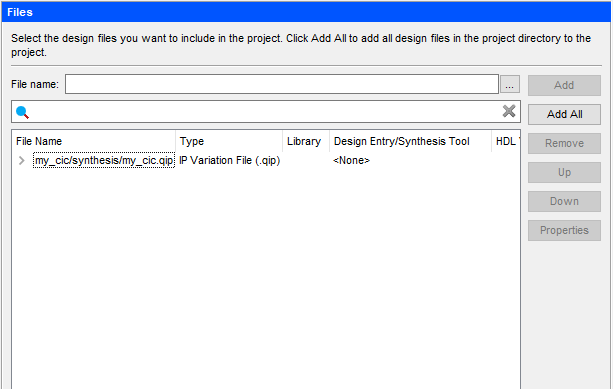

点击右上角的 ,在弹出来的窗口中,双击选择D:mdy_bookcic_prjmy_cicsynthesis目录下的my_cic.qip文件(注意不要搞错文件类型)。然后记得要点Add,才算正式加到工程。

,在弹出来的窗口中,双击选择D:mdy_bookcic_prjmy_cicsynthesis目录下的my_cic.qip文件(注意不要搞错文件类型)。然后记得要点Add,才算正式加到工程。

图583

点OK关闭本窗口。

IP核生成后弹出此对话框点击yes将此IP核添加进工程。

3.3.3例化CIC IP核

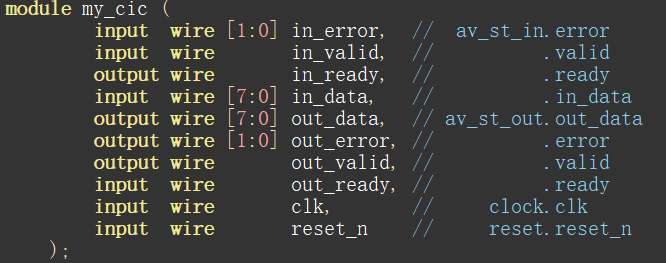

用GVIM打开D:mdy_bookcic_prjmy_cicsynthesismy_cic.v文件,该文件就是生成的CIC IP核文件。

图584

my_fir模块的各个信号的描述见下表。

|

信号名 |

I/O |

位宽 |

作用 |

|

clk |

I |

1 |

时钟输入信号。 |

|

reset_n |

I |

1 |

复位信号,低电平有效。 |

|

in_data |

I |

8 |

滤波器输入的数据输入。注意,输入的是有符号数。 |

|

in_valid |

I |

1 |

滤波器输入的数据有效指示信号。 |

|

in_error |

I |

2 |

输入数据错误指示信号。实在想不出有啥错误情况,所以此处直接填0。 |

|

in_ready |

O |

1 |

本IP核准备好信号。 |

|

out_data |

O |

8 |

滤波器的输出。注意,是有符号数。 |

|

out_valid |

O |

1 |

滤波器输出有效指示信号。 |

|

out_error |

O |

2 |

FIR滤波器输出错误指示信号。由于输入没错误,输出也不会有错误,所以可以忽略该信号,例化时不连接。 |

|

out_ready |

I |

1 |

下游模块准备好信号。当下游模块准备好时,本IP核才会输出一个数据。 可以利用此信号来控制IP核数据输出的频率。 |

无符号数转成有符号数的方法很简单:cic_din = sin_data - 128。读者有兴趣可以验证一下。

生成CIC IP核后,我们要对其进行例化,才行使用上这个IP核,例化名起名u_my_cic,cic的输出数据信号命名为cic_dout。

我们要控制CIC IP核的输出,使每个数据都能等间隔输出数据。由于CIC滤波器的输入是100个时钟一个数据,CIC是4倍速率,因此输出是25个时钟一个数据。所以我们每25个时钟给一个有效信号连到out_ready接口上。这时需要一个计数器cnt1来计时25个时钟,该计数器加1条件是“1”,结束条件是“数到25个”。

|

1 2 3 4 5 6 7 8 |

always @(posedge clk or negedge rst_n) begin if (rst_n==0) begin cnt1 <= 0; end else if(add_cnt1) begin if(end_cnt1) cnt1 <= 0; else cnt1 <= cnt1+1 ; end end assign add_cnt1 = 1; assign end_cnt1 = add_cnt1 && cnt1 == 25-1 ; |

有了这些信号后,就可以例化CIC IP核了。

|

1 2 3 4 5 6 7 8 |

assigncic_din = sin_data - 128; my_cic u_my_cic( .in_error (0 ), .in_valid (end_cnt0 ), .in_ready ( ), .in_data (cic_din ), .out_data (cic_dout ), .out_error ( ), .out_valid (cic_dout_vld), .out_ready (end_cnt1 ), .clk (clk ), .reset_n (rst_n ) ); |

3.4DA接口信号设计

接下来是设计信号dac_da。dac_da是直接输出正弦信号,但由于DA的输出电压与dac_da是成反比例线性关系,所以dac_da都是按(255-sin_data)得到。那么可以写出dac_da的代码。

|

1 2 3 4 5 6 7 8 |

always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin dac_da <= 0; end else begin dac_da <= 255 - sin_data; end end |

接下来是设计信号dac_sleep,AD是一直工作的,所以要让dac_sleep一直为0。

dac_clka为了满足tS的时间要求,可以让dac_clka = ~clk。

dac_wra可以与dac_clka相同。

|

1 2 3 |

assign dac_sleep = 0 ; assign dac_wra = dac_clka ; assign dac_clka = ~clk ; |

接下来是设计信号dac_db。dac_db是直接输出滤波后的信号cic_dout。但要注意的是cic_dout是有符号数(范围是-128~127),所以要转有无符号数(0~255)。假设转换后的信号为cic_dout2,则cic_dout2 = cic_dout + 128。另外,由于DA的通道2的输出电压与dac_db是成反比例线性关系,所以dac_db都是按(255-cic_dout2)得到。那么可以写出dac_db的代码。

|

1 2 3 4 5 6 7 8 |

assign cic_dout2 = cic_dout + 128; always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin dac_db<= 0; end else begin dac_db<= 255 -cic_dout2; end end |

dac_clkb为了满足tS的时间要求,可以让dac_clkb = ~clk。

dac_wrb可以与dac_clkb相同。

|

1 2 3 |

assign dac_wrb = dac_clkb ; assign dac_clkb = ~clk ; |

3.5信号定义

至此,模块主体已经完成。接下来是将module补充完整。

cnt0是用always产生的信号,因此类型为reg。cnt0计数的最大值为99,需要用7根线表示,即位宽是7位。add_cnt0和end_cnt0都是用assign方式设计的,因此类型为wire。并且其值是0或者1,1个线表示即可。因此代码如下:

|

1 2 3 |

reg [6:0] cnt0 ; wire add_cnt0 ; wire end_cnt0 ; |

cnt1是用always产生的信号,因此类型为reg。cnt1计数的最大值为24,需要用5根线表示,即位宽是5位。add_cnt1和end_cnt1都是用assign方式设计的,因此类型为wire。并且其值是0或者1,1根线表示即可。因此代码如下:

|

1 2 3 |

reg [4:0] cnt1 ; wire add_cnt1 ; wire end_cnt1 ; |

addr是用assign设计的,因此类型为wire。其值最大为7,一共有3根线,位宽为3;add_addr和end_addr都是用assign方式设计的,因此类型为wire。并且其值是0或者1,1根线表示即可。故而代码如下

|

1 |

wire [2:0] addr ; wire add_addr ; wire end_addr ; |

sin_data是用always设计的,因此类型为reg。其最大值为255,要有8根线表示,位宽为8,故而代码如下

|

1 |

reg [7:0] sin_data ; |

cic_din是用assign设计的,因此类型为wire。其位宽为8,故而代码如下

|

1 |

wire [7:0] cic_din ; |

cic_dout是例化模块的输出,非always设计的,因此类型为wire。其位宽为8,故而代码如下

|

1 |

wire [7:0] cic_dout ; |

cic_dout2是用assign设计的,非always设计的,因此类型为wire。其位宽为8,故而代码如下

|

1 |

wire [7:0] cic_dout2 ; |

dac_da是用always设计的,因此类型为reg。其位宽为8;dac_sleep是用assign设计的,因此类型为wire,位宽为1;dac_wra是用assign设计的,因此类型为wire,位宽为1;dac_clka是用assign设计的,因此类型为wire,位宽为1;dac_mode是用assign设计的,因此类型为wire,位宽为1。故而代码如下

|

1 |

reg [7:0] dac_da ; wire dac_sleep ; wire dac_wra ; wire dac_clka ; wire dac_mode ; |

dac_db是用always设计的,因此类型为reg。其位宽为8;dac_wrb是用assign设计的,因此类型为wire,位宽为1;dac_clkb是用assign设计的,因此类型为wire,位宽为1。故而代码如下。

|

1 |

reg [7:0] dac_db ; wire dac_wrb ; wire dac_clkb ; |

在代码的最后一行写下endmodule

|

1 |

endmodule |

至此,整个代码的设计工作已经完成。下一步是新建工程和上板查看现象。

4综合与上板

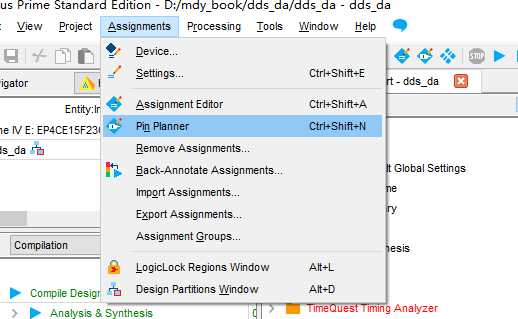

4.1添加文件到工程

图585

1.前面已经介绍了新建工程。现在打开quartus,在Project菜单中选择Add/Remove File to Project,弹出文件窗口。

图586

点击右上角的 ,在弹出来的窗口中,双击选择D:mdy_bookcic_prj目录下的cic_prj.v文件。然后记得要点Add,才算正式加到工程。

,在弹出来的窗口中,双击选择D:mdy_bookcic_prj目录下的cic_prj.v文件。然后记得要点Add,才算正式加到工程。

图587

点OK关闭本窗口。

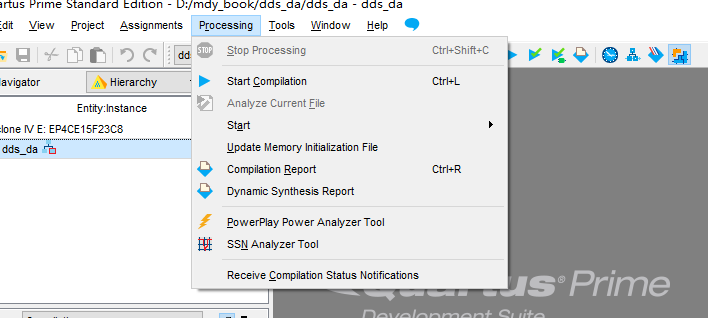

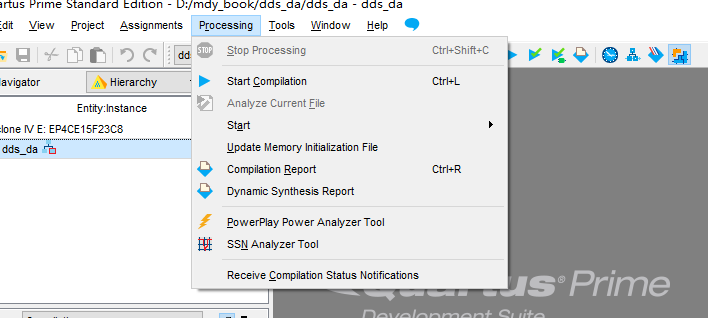

4.2综合

图588

在菜单栏中,选中Processing,然后选择Start Compilation,开始对整个工程进行编译和综合。

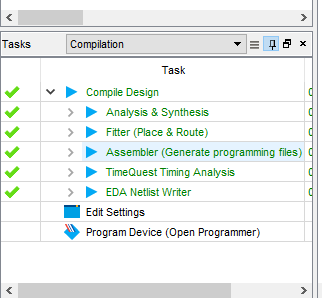

图589

出现上面的界面,就说明编译综合成功。

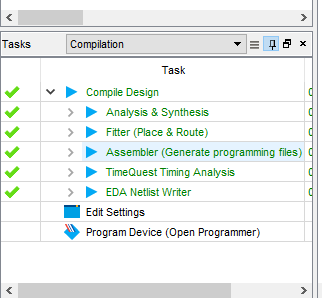

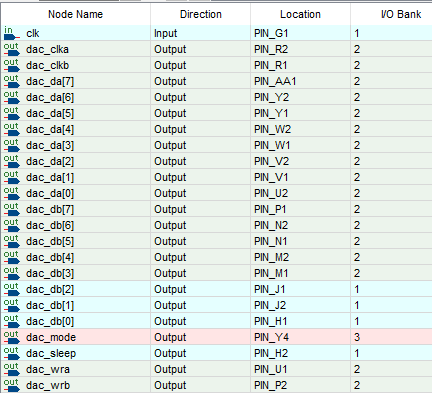

4.3配置管脚

图590

在菜单栏中,选中Assignments,然后选择Pin Planner,就会弹出配置管脚的窗口。

图591

在配置窗口中的location一列,可以填写每个管脚所对应的FPGA管脚号。

|

器件 |

AD9709管脚 |

原理图信号 |

FPGA管脚 |

FPGA工程信号 |

|

U8 |

MODE |

DAC_MODE |

Y4 |

dac_mode |

|

SLEEP |

DAC_SLEEP |

H2 |

dac_sleep |

|

|

CLK1 |

DA_CLKA |

R2 |

dac_clka |

|

|

WRT1 |

DA_WRA |

U1 |

dac_wra |

|

|

DB7P1 |

DAC_DA7 |

AA1 |

dac_da[7] |

|

|

DB6P1 |

DAC_DA6 |

Y2 |

dac_da[6] |

|

|

DB5P1 |

DAC_DA5 |

Y1 |

dac_da[5] |

|

|

DB4P1 |

DAC_DA4 |

W2 |

dac_da[4] |

|

|

DB3P1 |

DAC_DA3 |

W1 |

dac_da[3] |

|

|

DB2P1 |

DAC_DA2 |

V2 |

dac_da[2] |

|

|

DB1P1 |

DAC_DA1 |

V1 |

dac_da[1] |

|

|

DB0P1 |

DAC_DA0 |

U2 |

dac_da[0] |

|

|

CLK2 |

DA_CLKB |

R1 |

dac_clkb |

|

|

WRT2 |

DA_WRB |

P2 |

dac_wrb |

|

|

DB7P2 |

DAC_DB7 |

P1 |

dac_db[7] |

|

|

DB6P2 |

DAC_DB6 |

N2 |

dac_db[6] |

|

|

DB5P2 |

DAC_DB5 |

N1 |

dac_db[5] |

|

|

DB4P2 |

DAC_DB4 |

M2 |

dac_db[4] |

|

|

DB3P2 |

DAC_DB3 |

M1 |

dac_db[3] |

|

|

DB2P2 |

DAC_DB2 |

J1 |

dac_db[2] |

|

|

DB1P2 |

DAC_DB1 |

J2 |

dac_db[1] |

|

|

DB0P2 |

DAC_DB0 |

H1 |

dac_db[0] |

|

|

X1 |

|

SYS_CLK |

G1 |

clk |

|

K1 |

|

SYS_RST |

AB12 |

rst_n |

按上面配置好每个信号的管脚,其最终效果如下图。

图592

关闭Pin Planner,软件自动会保存管脚配置信息。

4.4再次综合

图593

在菜单栏中,选中Processing,然后选择Start Compilation,开始对整个工程进行编译和综合。

图594

出现上面的界面,就说明编译综合成功。

4.5连接开发板

图595

连接示意如上图所示。将电源接上开发板;USB BLASTER一端连接到JTAG插口,另一端连到PC的USB接口;将开发板上的P7接口和P11与示波器的两个通道相连。最后再将电源打开。

4.6上板

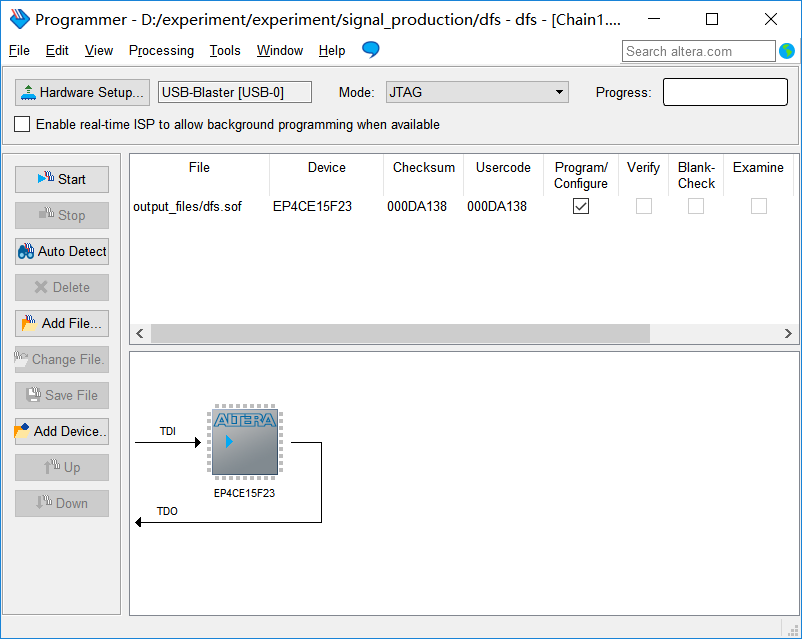

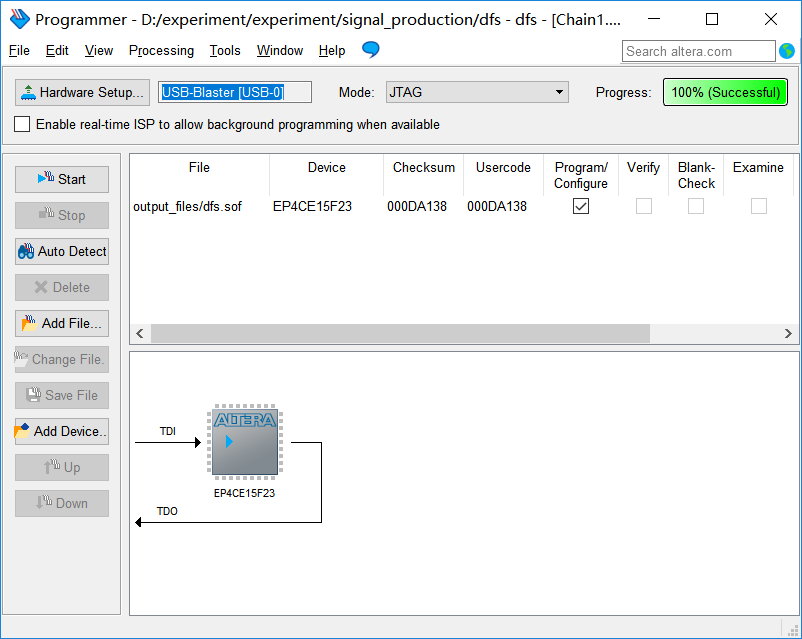

图596

在quartus的Task窗口中,右键Program Device选择Open进入烧录界面。

图597

在上面的界面中,默认会选中文件output/cic_prj.sof,

在上面的界面中,Hardware Setup的旁边会显示:USB-Blaster。

图598

点击statr,在progress这一条显示100%即表示成功,此时可以看FPGA输出效果了。