本文的文档编号:001500000032

需要看对应的视频,请点击视频编号:001300000078

1、本章主要介绍在FPGA的开发过程中,在逻辑代码上板运行前都会进行仿真验证。

2、本章主要介绍一个实时的信号分析工具获取FPGA内部的实时信号从而进行调试分析——SignalTap的工作原理、使用流程,并且通过3个案例又对SignalTap的使用步骤进行了详细说明。

3、这是ALTERA的文档

第五章 SIGNALTAP调试工具

SignalTap是由Altera公司开发的一个在线、片内信号分析的工具,为设计开发者验证所用。

我们什么时候会用到signalTap呢?当代码经过仿真没有问题,但加载到FPGA电路板后,发现功能不正确时,我们就可以用signalTap工具进行分析, 它的作用就类似于一个数字逻辑分析仪。利用signaltap基本上可以代替数字逻辑分析仪了 ,它是quartus里最常用的工具,同学们必须熟练使用这个工具。

1 软件介绍和原理

需要看对应的视频,请点击视频编号:001300000079

在使用signalTap前,我们先理解一下SignalTap的原理, 这样就助于理解每个参数。

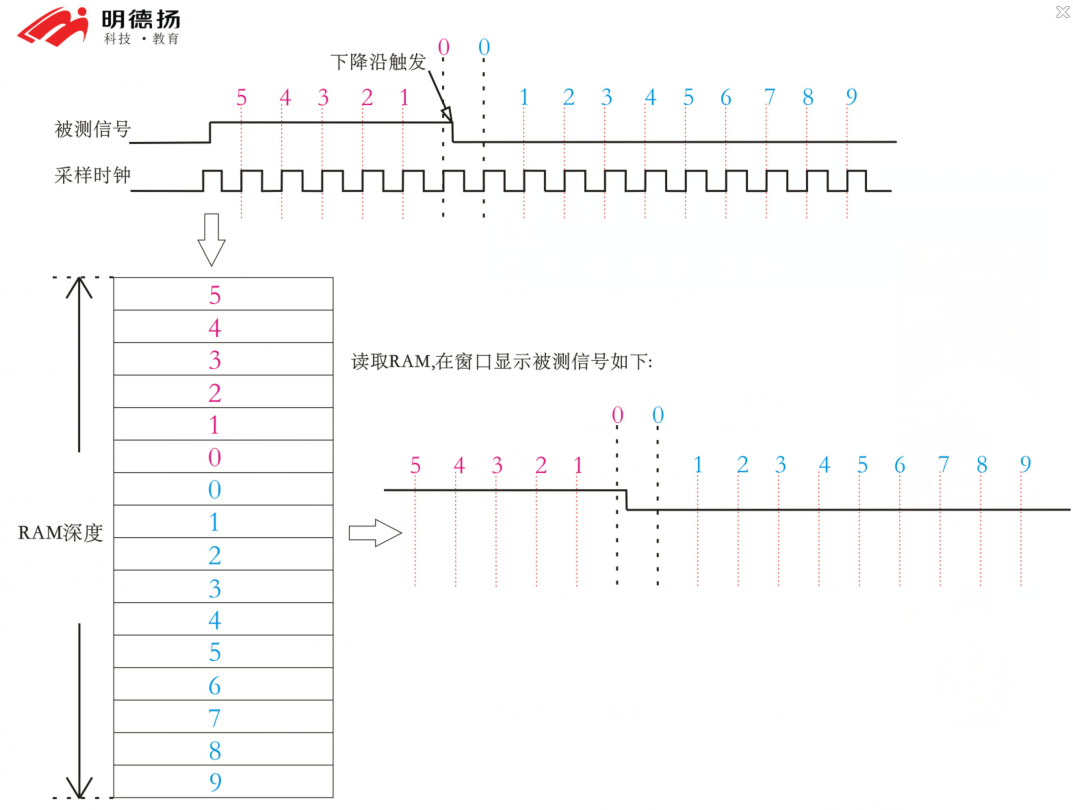

图 77

如图为SignalTap II的基本工作原理,通过此图也能很好的理解触发条件、采样时钟、采样深度等的概念(概念 及相关设置见第三节)及其之间的关系。

需要观察分析的信号,我们称之为“被测信号”(可以有 多个),SignalTap II的基本工作过程如下:以被测信号为对象,根据需要设置合理的触发条件,在触发条件(如图中的被测信号下降沿)满足时的前后一段时间,每个采样时钟的上升沿都会对被测信号进行一次采集,并将采集的信号值存储在内部的RAM中。我们可以指定触发条件前后采多少个样点,如果RAM比较大,那么可以保存的数据就比较多,如果RAM比较小,那么保存的数据自然少,RAM大小决定了观察数据的多少。

最后SignalTap将读出RAM中的数据,并逐个在显示器中显示出来(因此SignalTap看到的都是理想的,没有毛刺的信号),达到了我们对信号进行在线调试分析的目的。

2 软件界面

需要看对应的视频,请点击视频编号:001300000080

打开Quartus后,在菜单栏中,选择“Tools”- >”SignalTal II Logic Analyzer”,就可以打开SignalTap工具。如下图:

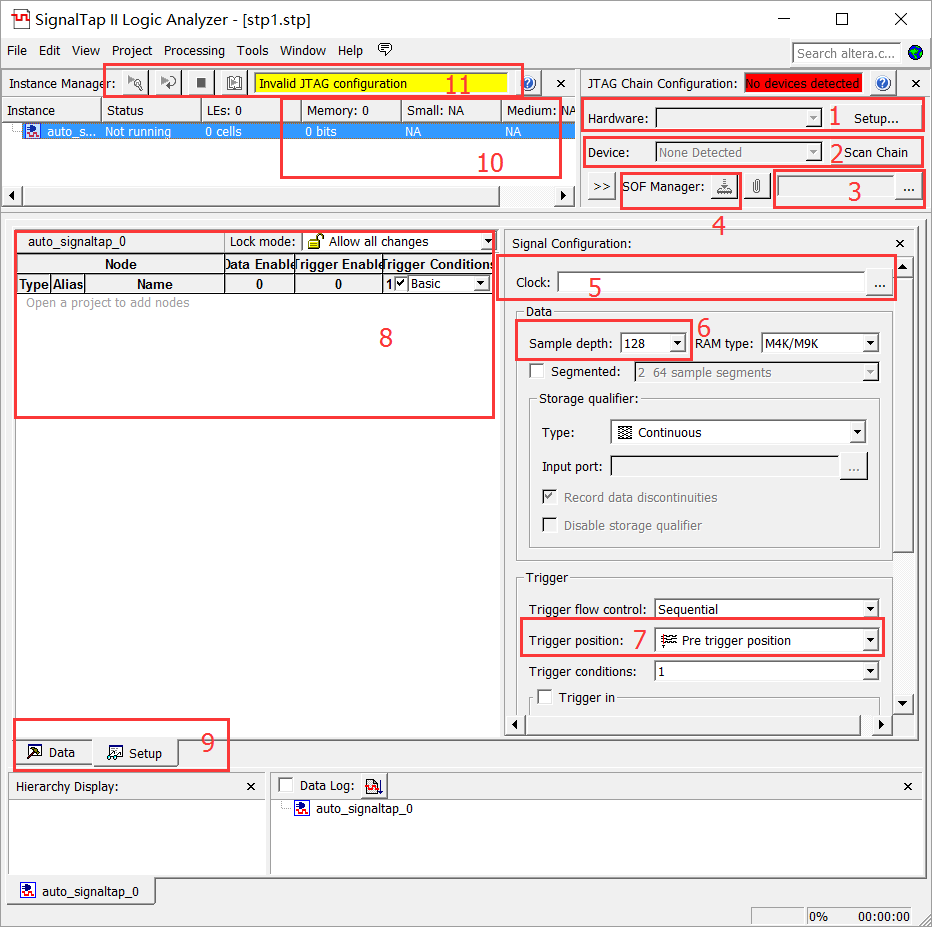

图 78

图 79

◆ 1—4为基本的软硬件配置。

1下载线选择;2硬件检测(识别相关的FPGA设备);3工程配置文件选择(sof文件);4加载sof文件(1-3均完成后即可加载文件)。

◆ 5—7为采样设置。

5选择采样时钟,采样时钟要根据具体需要进行设置 , 可以为模块的工作时钟,也可以为内部信号;

◆ 6为采样深度设置,采样深度并非越大越好,要根据分析需求进行合理设置;

◆ 7为触发位置选择,包括前段触发、中间触发、后端触发三种方式,以触发点为参考,触发位置不同,我们能得到不同时间段的信号值。

◆ 8—9为信号设置,包括添加信号,设置信号触发条件等。在8中空白处双击即可添加信号界面,根据需要添加工程中的相应信号,添加信号后即可设置其触发条件。

◆ 10为资源使用情况指示,如果资源多于FPGA本身的资源,综合时会报错,无法进行分析。

◆ 11为运行操作按钮,开始运行后,待触发条件满足后会显示波形。

3 上板例程

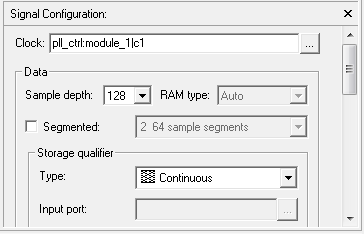

a、选择下载线、fpga芯片型号、工程配置文件

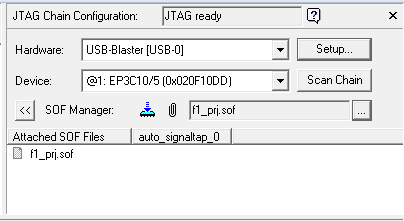

图 80

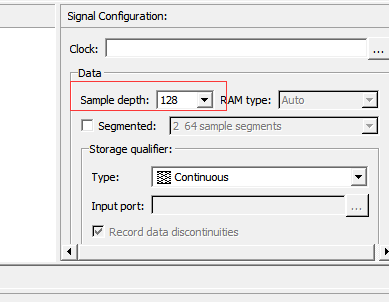

b、设置采样时钟、采样深度

图 81

这里我们选择内部pll的输出信号c1作为采样时钟,注意采样时钟不一定是工程里的时钟,内部任何信号都可以是采样时钟。

这里我们将采样深度设置为128个。也就是我们总共能看到128采样点的数据。

c、选择采样信号

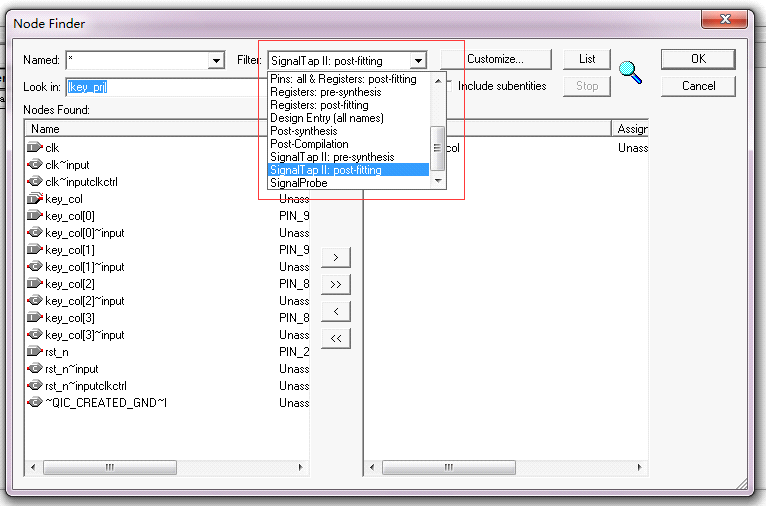

在setup窗口中,双击空白地方,弹出如下界面

图 82

红色框是选择哪个阶段的信号,例如是综合前、综合后等 ,因为综合时会优化,有些信号可能会找不到。我们一般选择pre-synthesis或Design Entry(all name)。

在Nodes Found选择我们要观察的信号,添加到右边框即可 。

本例我们这里选择key_col和rst_n信号来观察。

图 83

d、设置触发条件

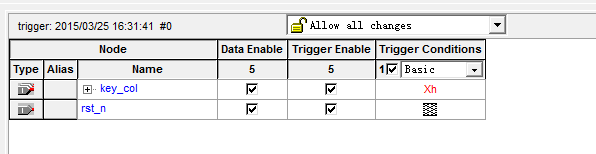

选择好信号后,即可进行触发条件的设置。

观察trigger Conditions一列,key_col的默认值为xh(总线型信号的don’t care ),rst_n的默认值为don’t care。在trigger Conditions一列中,右击rst_n所在的行,将出现6种触发条件供选择。

图 84

6种触发条件的含义如下:

don’t care:表示不关心,也即任意,此信号的值不影响触发条件;

Low :低电平触发;

Falling Edge:下降沿触发;

Rising Edge:上升沿触发;

High:高电平触发;

Either Edge:双沿触发,即有变化时触发。

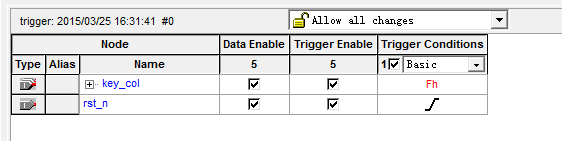

假设取上升沿触发,并对key_col也做触发条件的设置如下:

图 85

此时的触发条件含义为:当rst_n为上升沿并且 key_col全为高时触发。注意,这里多触发条件之间默认的是“与 ”的关系,很多人会误认为是“或”的关系。

e、综合并下载,点击“Run Analysis”按钮,观看结果

如果触发条件成立,则可在Data窗口观察到采样波形 ,此处是某一工程的采样结果,可以看到,其与modelsim波形是很相似的。

点击波形,则可以放大波形观看;右击波形,则是缩小波形。

图 86

4 案例说明

需要看对应的视频,请点击视频编号:001300000081

案例 1:SIGNALTAP的采样时钟,不一定是时钟信号,可以是其他任意的信号。总之,SIGNALTAP会在采样时钟的上升沿去捕捉信号的值,如果没有上升沿,则会一直等待。例如下图,就是以按键信号key为采样时钟。在key由0变1时,就会采样一个值。

案例 2:我们可以改变采样的深度,以便观察到信号更长时刻的值。下面的深度设置成128,这意味着,一共可以看到128个点的值。如果不够,可以设置成更大。但注意的是,SIGNALTAP需要RAM来保存采样的数据,所以采样深度越大,需要的RAM越大,这需要占用FPGA的资源,而有些FPGA是有限的。如果不支持这么大的RAM,在编译时会提示错误的。

图 87

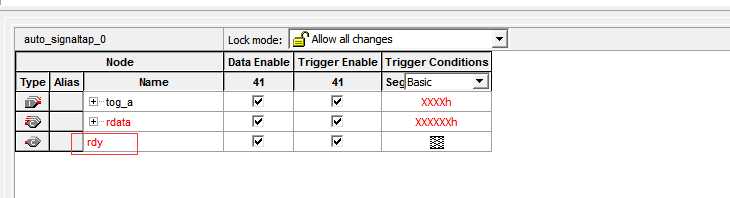

案例3:通过设置segmented,可以检查满足触发条件的次数。例如,发现按键有时候失灵的情况,为了定位此问题,我想检查按键按下的次数,是否与捕捉到信号次数一致。其主要设置为:

1. 把segmented设置为32;

2. 把捕捉到信号key_vld拉到显示窗口,该信 号为1表示捕捉到一个按键。

3. 设置触发条件为:key_vld的上升沿;

4. 按下run键,等待触发条件满足;

5. 按下按键4次。

6. 按停止捕捉键。

如果此时 SIGNALTAP出现5个窗口,其中前4个表示条件满足捕捉到的窗口,则表示近下按键的次数,与捕捉到的次数一致。否则,就是有错误。

案例 4:当添加信号后,该信号显示红色,如下图所示。表示该信号的捕捉将会有问题。

图 88

出现该问题的可能性原因有:

1. 该信号在电路综合时被优化。

a) 该信号虽然产生了,但没有被当作条件使用,或 者不是输出信号。说明该信号是多余的,所以综合时把该信号优化掉。

b) 如果认为该信号是有用的,不应该被优化掉。那说明电路有BUG,需要你去定位。

2. 组合逻辑信号一般是捕捉不到的。解决方法:那就不看这个信号,可以把产生这个信号的所有条件都抓出来,从而推敲结果是否正确。

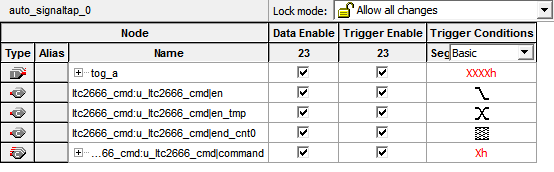

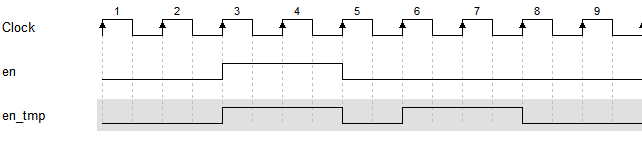

案例 5:下面的触发条件是:当en下降沿,并且en_tmp有变化。注意,是采样时钟上升沿时,同时两个条件满足才能触发。

图 89

图 90

上面波形中,第5时钟上升沿时,看到en=1,en_tmp等于1,不满足条件。而在第 6时钟时,发现en的下降沿(之前为1,现在为0),en_tmp的下降沿(之前为1,现在为0)。所以只有第 6时钟才满足触发条件。