本文为明德扬原创及录用文章,转载请注明出处!

本文的文档编号:000800000013

本文档没有对应的视频

1、本文是讲解了如何使用至简设计法来时序1位LED灯间隔1秒,亮N秒(其中N=1 .2. …. 9)的功能

个人总结及感悟:

对于学习本案例,首先要理解案例的顶层框架,再是理解框架下面的逻辑,最后才是理解代码。这一点对于自己动手写代码也很有帮助,毕竟写代码就是为了实现框架。再来说说本案例中的代码吧,本案例给出的代码对于刚接触FPGA的人也许会有“这代码写的太麻烦了吧!”“明明可以写成49_999_999的为啥要写成50_000_000-1呢?”之类的想法,这也是我刚接触明德扬的代码时的想法。

后来接触多了,自己也开始用明得扬的代码规范写了一些代码,才慢慢觉得明德扬的代码规范挺好用的,写出来的代码也通俗易懂。而且这些代码也很方便移植与修改,对于实现某些相似的功能时也不用自己再重新写代码,可以直接拿过来再修改一下就行了。

总的来说,要想学好FPGA需要从三个方面着手:1、框架;2、规范;3、动手做。这三个方面做好了,那以后自己做工程就成功一半了。

设计目标:

使用一个LED灯,实现闪烁灯的功能。工作时钟50M,也就是时钟周期为20ns。输出低电平时,灯亮;输出高电平时,灯灭。

功能要求:

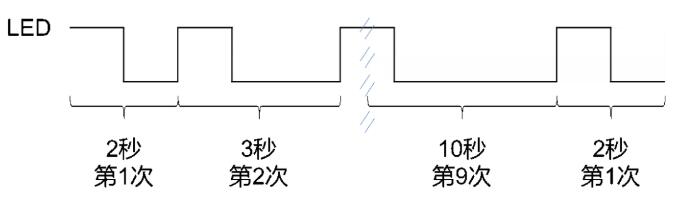

隔1秒,亮N秒。N的变化是1,2,3,……,9秒。然后再次循环。

波形示意图:

顶层信号设计:

工程共需要三个信号,时钟clk,复位rst_n和输出信号led。其中clk、rst_n是输入信号,led是输出信号,并且三个信号都是1比特的。

工程实现思路:

从功能要求及波形图可知,需要一个计数器计数第N次,需要一个计数器计数第N次需要持续的时间。本工程设计两个计数器cnt0,cnt1。cnt0用于计数第N次需要持续的时间,cnt1计数第N次。第1次时,持续2秒;第2次时,持续3秒;第N次时,持续N+1秒。直至第9次结束,又从第1次开始循环。输出信号led同时满足cnt0计数器的计数开始信号add_cnt0的出现与cnt0计数到50_000_000-1这两个条件时变为低电平;在end_cnt0信号出现时变为高电平,意味着在第N次计数中第1秒内灯灭,其余时间灯亮。

代码实现:

计数器cnt0

always@(posedgeclkor negedgerst_n)begin

if(rst_n)begin

cnt0<=0;

end

else if(add_cnt0)begin

if(end_cnt0)

cnt0<=0;

else

cnt0<=cnt0+1;

end

end

assign add_cnt0 = 1;

assign end_cnt0 = add_cnt0&&cnt0==x-1;

因为cnt0需要不停的计数,永不停止,故计数开始信号add_cnt0一直为1。引入了变量x,x为要计数的个数。比较计数器cnt1的不同,从而赋予变量x不同的值。

cnt1计数器

always@(posedgeclkor negedgerst_n)begin

if(rst_n)begin

cnt1<=0;

end

elseif(add_cnt1)begin

if(end_cnt1)

cnt1<=0;

else

cnt1<=cnt1+1;

end

end

assignadd_cnt1 = end_cnt0;

assignend_cnt1 = add_cnt1&&cnt1==9-1;

当计数器cnt0计数结束时的下一个时钟节拍里,使得cnt1计数加1。

led输出信号

always@(posedgeclkor negedgerst_n)begin

if(rst_n)begin

led<= 1;

end

elseif(add_cnt0 && cnt0 ==50_000_000-1)begin

led <= 0;

elseif(end_cnt0)begin

led <= 1;

end

end

led信号在第N次计数时,计数1秒后灯亮。

信号定义:

always里面的信号需要定义为reg型;assign的信号需要定义为wire型。另外需要重点注意每个信号的位宽。

注意事项:

具体编写代码过程中,需要注意以下三点。

1、要注意计数器的计数结束条件,例如工作时钟是50M,计数1秒钟,那么计数范围就是0~49_999_999,千万要注意不能超出。

2、代码一定要规范,不然过段时间可能连自己都看不懂。

3、要注意各个信号的位宽。