|

本节的文档编号:001100000061

需要看对应的视频,请点击视频编号:001100000064 1、本节主要进行组合逻辑的介绍,包括:程序语句(assign语句、always语句),数字进制(二进制、不定态、高阻态),算数运算符(加、减、乘、除运算符),逻辑运算符(逻辑与、或、非运算符),按位逻辑运算符(单目按位与、或、非运算符,双目按位与、或、异或运算符),关系运算符,移位运算符(左移、右移运算符),条件运算符(三目运算符、if语句、case语句、选择语句等),拼接运算符;

2、ALTERA和VIVADO文档 5.7 移位运算符

在Verilog HDL中有两种移位运算符,分别为“<<”(左移位运算符)和“>>”(右移位运算符)。

下面分别介绍两者的用法:

5.7.1左移运算符

在Verilog HDL中,用“<<”表示左移运算符。其一般表达式为:

A<< n;

其中,A代表要进行移位的操作数,n代表要左移多少位。此表达式的意义是把操作数A左移n位。 左移操作属于逻辑移位,需要用0来填补移出的空位,即在低位补0。左移n位,就要补n个0。

以上代码由于左移了2位,所以在低位补2个零,所以上面代码运行结果是:a = 4’b1100。

左移操作中有以下三点值得注意的地方:

(1)左移操作是不消耗逻辑资源的,甚至连与门、非门都不需要,它只是线的连接。

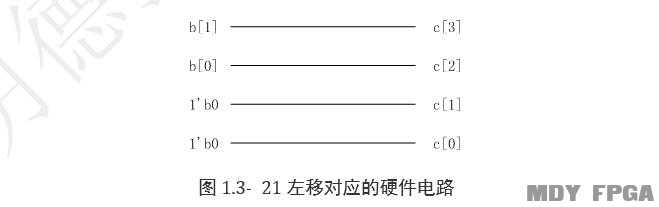

上面代码是将信号b左移两位并赋给c,其所对应的硬件电路如下图:

(2)左移操作需根据位宽储存结果

读者在学习过程中可能看到过如下代码:

4’b1001<<1=4’b0010与4’b1001<<1=5’b10010

为什么操作数同样是4’b1001,都是左移一位,但结果一个是4’b0010,一个是5’b10010呢?

这是因为左移操作后,要看用多少位来存储结果。

上面代码中由于a是4比特,只能保存4位结果,所以b左移1位赋给4 bit的a, 用0填补移出的位后结果为a = 4’b0010 ;

而上面代码中由于a是5比特,能保存5位结果,所以b左移1位赋给5 bit的a, 用0填补移出的位后结果为a = 5’b10010 ;

(3)左移操作的操作数可以是常数,也可以是信号。同样,左移操作的移位数、常数也可以是信号。

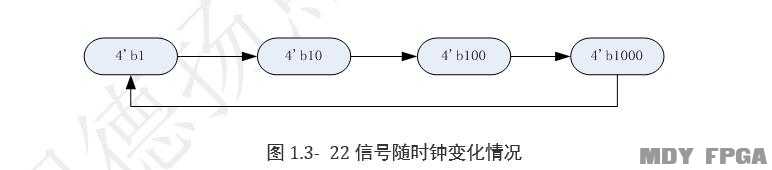

上面代码中cnt每个时钟加1,由于是3比特,所以值为0~2。a则是4’b1左移cnt位。 当cnt等于0时左移0位,a等于4’b1;当cnt等于1时左移1位,a等于4’b10。以此类推,a的每个时钟变化情况如下所示:

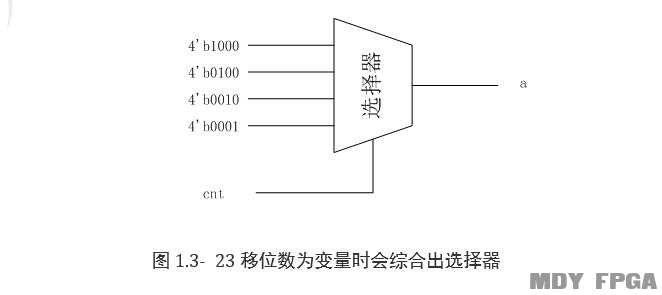

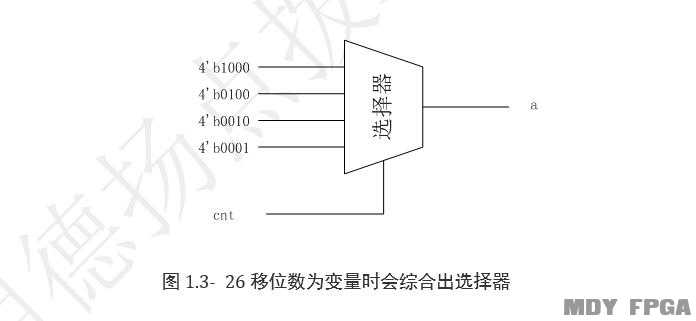

需要注意的是,当移位数是信号时,其综合的电路并不是简单的连线,可能会综合出如下图所示的选择器。 然而即便如此,这种硬件电路所消耗的资源依然比较少。

5.7.2右移运算符

在Verilog HDL中,用“>>”表示右移运算符。其一般表达式为:A >>n;

其中,A代表要进行移位的操作数,n代表要右移多少位。此代码表示的意义是把操作数A右移n位。

在右移操作中有以下三点值得注意的地方:

(1)右移操作属于逻辑移位,需要用0来填补移出的空位,即在高位补0,补多少个0, 取决于保存结果的信号的位宽。

4’b0111右移两位后的结果为2’b01,由于a是6位的,2位赋值给6位需要在高位补0, 因此需要补4个0。所以上面代码运行结果是:

a = 6’b0001

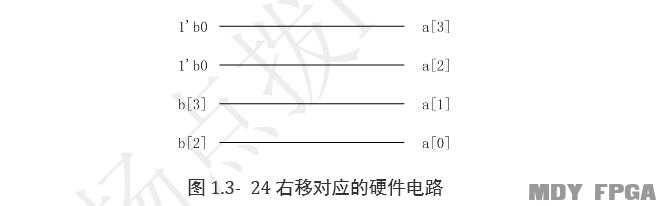

(2)与左移操作相似,右移操作是不消耗逻辑资源的,甚至连与门、非门都不需要,其只是线的连接。

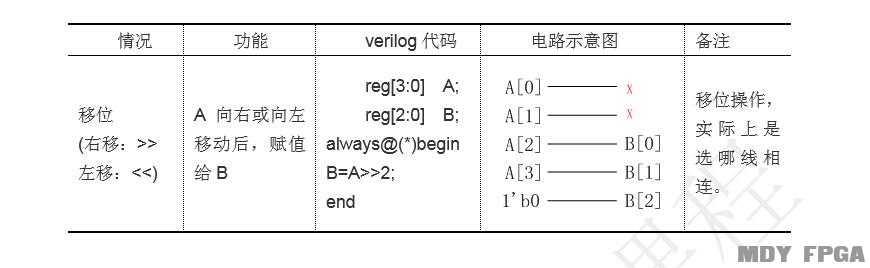

上面代码是将信号b左移两位并赋给a,其所对应的硬件电路如下图所示。

(3)左移操作的操作数可以是常数,也可以是信号。同样,右移操作的移位数可以是常数,也可以是信号。

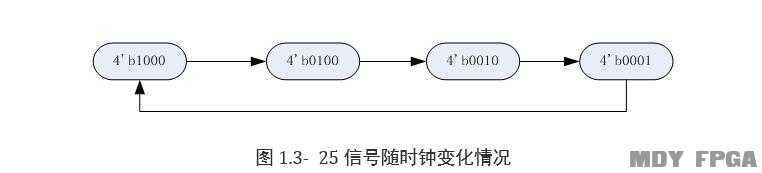

上面代码中,cnt每个时钟加1,由于是3比特,所以值为0~2。a则是4’b1000右移cnt位。 当cnt等于0时右移0位,a等于4’b1000;当cnt等于1时右移1位,a等于4’b0100。以此类推, a的每个时钟变化情况如下图所示。

与左移操作类似,在右移操作中,如果移位数是信号时,其综合的电路就不是简单的连线, 而是有可能会综合出如下图所示的选择器。然而同样在这一情况下,这种硬件电路所消耗的资源依然比较

少。

FPGA中要尽量避免乘法运算,因为这种计算需要占用较大的硬件资源,并且运算速度较慢。 当不得不使用乘法的时候,尽量乘以2的N次方,这样在设计中可以利用左移运算来实现该乘法运算, 从而大大减少硬件资源。 当乘数是2的N次方的常数时可以用移位运算来实现乘法。例如:a*2, 等价于 a<<1;a*4等价于a<<2;a*8等价于a<<3,依此类推。

即使乘数不是2的N次方的常数,也可以通过移位运算来简化实现。例如:

上面代码中b和c都可以实现a*127,但第1行消耗了一个乘法,而第2行则只用到一个减法器。

上面代码中,b和c都可以实现a*67,但第1行消耗了一个乘法,而第2行则只用到两个加法器, 从而节省了资源。 有读者可能注意到,上面两个例子中的乘数都是常数,那么在设计时这种乘法也要花时间和精力来考虑优化吗? 其实是不必要的,因为现在综合工具都很强大,当工具发现乘数是常数时会自动按上述过程进行优化, 也就是说乘以常数在实质上并不消耗乘法器资源,读者可以放心使用。 但当出现乘数不是常数的情况时,读者就要注意乘法的使用了。尽量将信号转换为与2的N次方相关的形式。 例如当数据要扩大后来计算时,不要按照惯有思维将数据扩大100倍,而是应该直接将其扩大128倍。

FPGA设计中要极力避免除法,在笔者眼中甚至是严禁使用“ /”来用于除法计算。 这是由于除法器会占用极大的资源,其占用资源量要多于乘法器,而且很多时候不能在一个时钟周期内得出结果。 而当不得不使用除法的时候,读者应尽量使除法转化为除以2的N次方形式, 这样便可以利用右移运算来实现该除法运算,从而大大减少硬件资源。 当除数是2的N次方的常数时,就可以用移位运算来实现除法。 例如:a/2,等价于 a>>1;a/4等价于a>>2;a/8等价于a>>3,依此类推。

与左移不同的是,当除数不是2的N次方的常数时,不能简单地通过移位运算来简化实现。

总而言之,在FPGA设计中应尽力避免除法。

独热码,也叫one-hot code,就是只有1个比特为1,其他全为0的一种码制。 例如8’b00010000,8’b1000000等。 独热码在设计时非常有用,可以用来表示状态机的状态使状态机更健壮, 也可以用于多选一的电路中,表示选择其中的一个。 利用左移位操作,可以方便地产生独热码,例如产生4’b0010,可以是4’b1 << 1。 类似地,也可以产生1个比特为0,其他为1的码制。例如产生4’b1011,可以是~(4’b1<<2)。 利用左移操作,还可以产生其他需要的数字结果:

例如,产生5’b00111,可以是(5’b1<<3)-1。

|