Cyclone V GT FPGA 开发板

(DK-DEV-5CGTD9N)

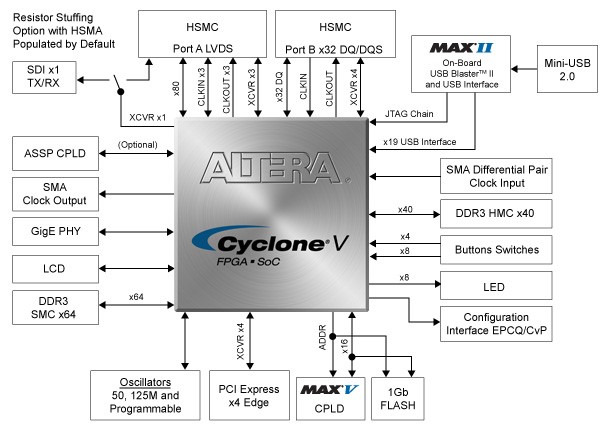

英特尔® Cyclone ® V GT FPGA 开发套件可用于对 Cyclone V GT FPGA 或 Cyclone V GX FPGA 应用进行原型设计。它提供了一种快速简单的方法来开发低成本、低功耗的 FPGA 系统级设计并快速获得结果。该套件支持无数功能,例如:

- FPGA原型制作

- FPGA 功率测量

- 收发器 I/O 性能高达 5.0 Gbps

- PCI Express ® (PCIe ® ) Gen2 x4(每通道 5.0 Gbps)

- 端点或根端口支持

开发套件内容:

1.特色设备

- Cyclone V GT FPGA—5CGTFD9E5F35C7N

- MAX ® V CPLD—5M2210ZF256(系统控制器)

- MAX II CPLD—EPM570GT100C3N(板载 USB Blaster TM II)

- MAX II CPLD—EPM570ZM100(ASSP CPLD 封装)

2. 配置

- 嵌入式 USB-Blaster II (JTAG)

- 快速无源并行 (PFL)

- Intel EPCQ—EPCQ256SI16N(四串行配置设备)

3. 存储设备

- 384 MB x40 硬核内存控制器 (HMC) DDR3 SDRAM,带纠错码 (ECC)

- 512 MB x64 软内存控制器 (SMC) DDR3 SDRAM

- 1 Gb x16 同步闪存

4. 标准通讯端口

- PCIe x4 边缘连接器

- 千兆以太网 (GbE)

- 1 个 SMA 时钟输出

- 两个通用高速夹层卡 (HSMC) 连接器,每个连接器都有四个高速串行收发器通道

- 1 个串行数字接口 (SDI) 通道 — 1 个 SMB 用于 RX,1 个 SMB 用于 TX

- 通过电阻填充选项与 HSMA 共享通道

5. 按钮、DIP 开关和 LED

- 计时

- 用于 FPGA 参考时钟输入的可编程时钟发生器

- 用于 FPGA 参考时钟输入的 125 MHz LVDS 振荡器

- 用于 FPGA 参考时钟输入的 148.5/148.35 MHz LVDS VCXO

- 用于 FPGA 和 MAX V CPLD 时钟输入的50 MHz 单端振荡器

- 用于 MAX V CPLD 配置时钟输入的100 MHz 单端振荡器

- SMA 输入 (LVPECL)

6. 力量

- 笔记本电脑直流输入 14 – 20 V 适配器

- PCIe 边缘连接器

7. 系统监控电路

- 功率(电压、电流、瓦数)

8. PCIe 卡标准尺寸 (4.376" x 6.600")