本文为明德扬原创文章,转载请注明出处!

在我们的LVDS车载视频拼接项目中,主机发送LVDS信号给FPGA,FPGA经过解串将LVDS串行数据转换为7路并行数据,并将并行数据进行RGB三通道映射,LVDS信号中的RGB信号与外部摄像头采集到的RGB信号做拼接然后再将7路并行数据转换成串行数据输出给车载屏幕。

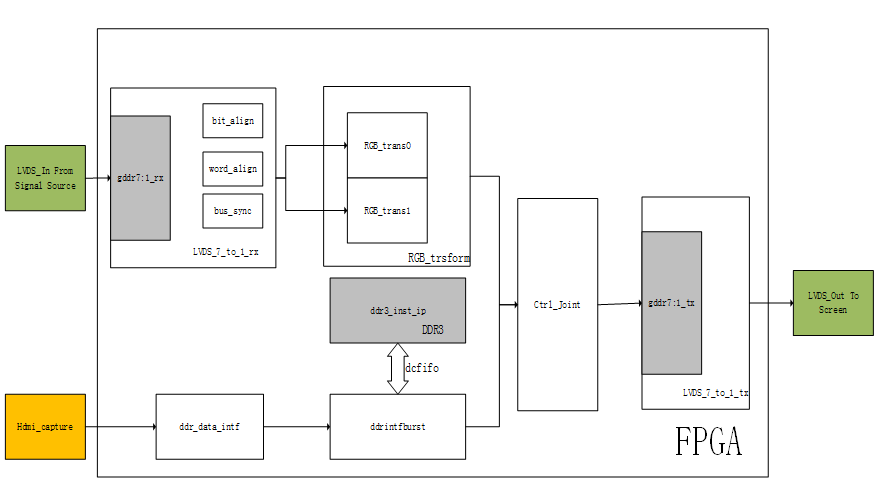

一、项目结构图

该项目的结构图如下图1所示:

二、实现功能

该项目使用的是Lattice芯片,开发工具为Diamond,需要使用到两个接口,一个是LVDS接口,一个是DDR3接口。主机发送的是2对4Lane、7bit视频数据。7bit串行数据经过LVDS_7_to_1_rx模块转换为7路并行数据,在此模块中需要使用到GDDR7:1 IP核,该IP核的作用就是进行LVDS串行数据的解串,具体的生成以及例化教程我在前面的文章中已有详细的介绍。解串后的数据要进行同步和初始化从而确保输出的数据是对齐的。解串后的4Lane、7bit数据共28bit,包含了三通道信号RGB888、行场同步信号Hsync和Vsync、以及输入有效信号DE。并行数据经过RGB_trasform模块进行RGB三通道映射,并与摄像头采集到的RGB信号进行拼接。摄像头采集的信号通过DDR3的接口模块ddrinfburst送入DDR3中,在需要进行数据拼接的时候再从该模块将数据取出进行图像的拼接,拼接完成后的7路并行数据再通过LVDS_7_to_1_tx模块变换为7bit的串行数据输出到外部显示屏上。

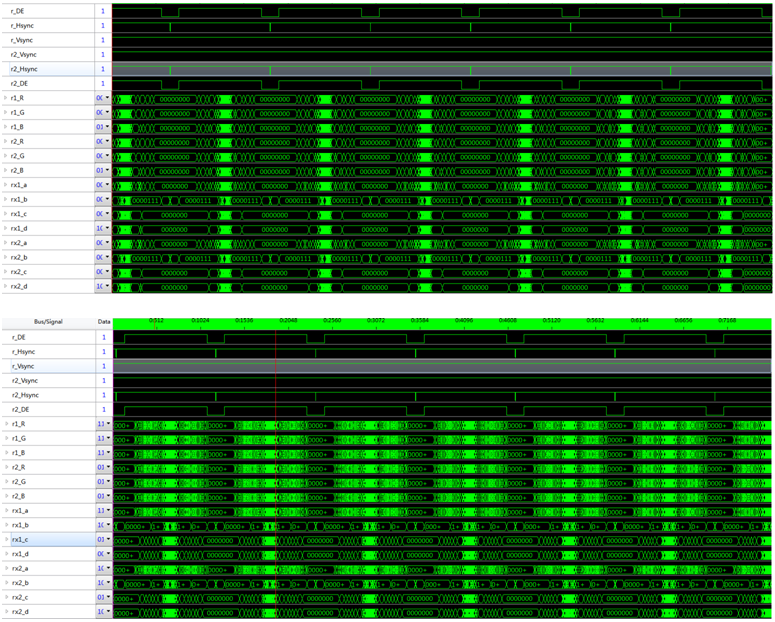

三、接口数据波形

其中,外部主机输入进来的LVDS信号抓取到的波形图如下:

图2 LVDS信号抓取到的波形图

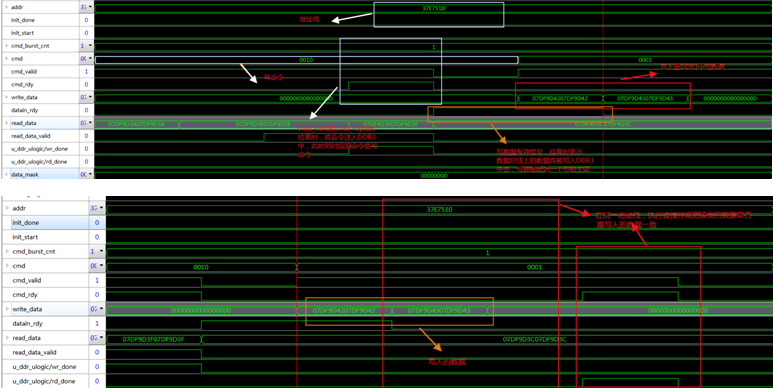

DDR3实现正确读写波形图如下:写数据:

图3 写入到DDR3数据

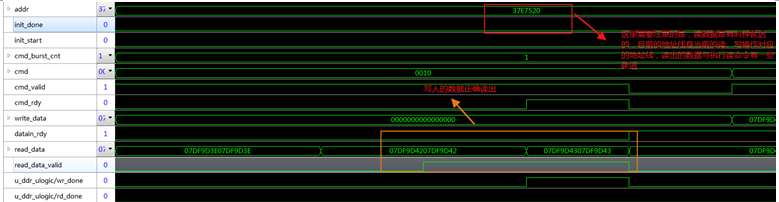

读数据:

图4 从DDR3读出数据

如对我们的项目感兴趣,可以加QQ 3358622769 与我进行更深入的讨论!