作者:鱼丸粗面

本文为明德扬原创文章,转载请注明出处!

在上一篇的文章《1.LATTICE DIAMOND的LICENSE申请方法》中,我为大家详细介绍了Lattice开发工具Diamond的安装以及license生成方法。Diamond开发工具下载链接在明德扬的官方论坛上已经更新,有需要的同学请到官方论坛自取。Diamond 3.10开发工具下载传送门:

http://www.fpgabbs.cn/forum.php?mod=forumdisplay&fid=58。

首先了解一下软件界面。工程生成后,会在File List状态栏中显示工程的芯片型号、工程文件、管脚配置文件、调试文件、以及编译后的文件等信息(如下图1):

图1 File List界面信息

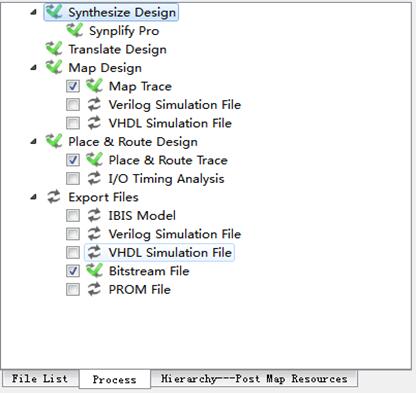

Process状态栏显示的是工程的综合、生成下载文件过程,其中包括工程的综合、布局布线,和待烧录文件的生成(如下图2)。Hierarchy状态栏可以用来查看添加的IP核有没有编译进工程中。

图2 Process界面信息

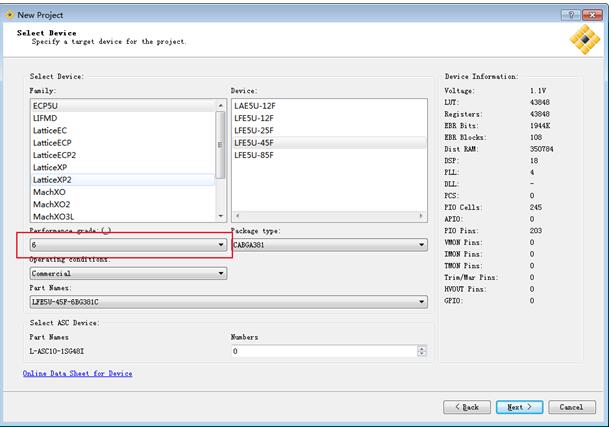

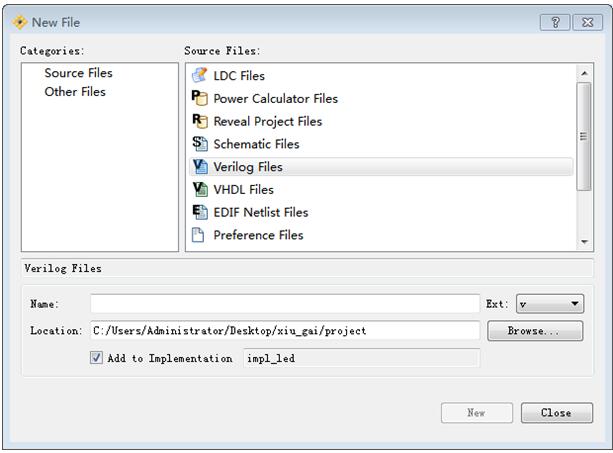

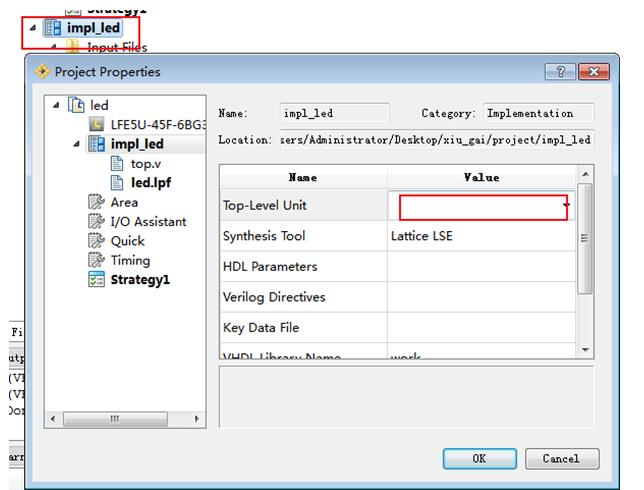

下面来新建一个工程。Diamond建立工程的过程与Quartus类似,点击File→New→Project来打开工程建立窗口。在Project Name界面中分别为工程和综合后的文件命名以及选择保存的文件位置;在Select Device界面对FPGA芯片进行选择,在要编程的FPGA芯片系列下找到对应的型号,这里需要注意的是芯片的速度等级要与实际的芯片型号对应上,否则烧录的时候会出现错误(如下图3)。Select Synthesis Tool界面选择编译工具,这里选择Diamond自带的编译工具Lattice LSE,也可以选择外部编译工具Synplify Pro。工程生成之后,会在File List界面显示工程的芯片信息、工程文件等。工程建立后,需要添加文件,右键点击Input Files→Add→New File,在弹出的窗口中选择Verilog Files(或VHDL Files),选择好文件目录和文件名,即可添加一个空白的文件(如下图4)。设计好各个模块后,需要指定一个顶层文件,右键点击Impl_xx(如下图5),在弹出的界面中找到Top-Level Unit,在右侧空白栏中输入需要设置为顶层模块的名称即可。

图3 芯片选型界面

图4 添加V文件

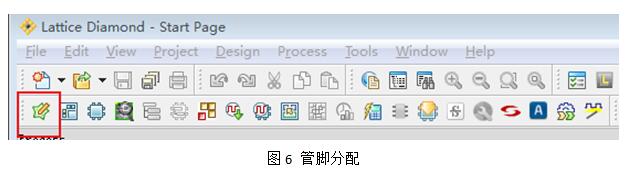

工程文件建立好后,需要编译一下,在第二栏Process中双击Synthesis Design对工程进行编译。编译通过后需要分配管脚,找到界面上方工具栏第三行最左侧图标SpreadSheet View(如下图6)进行管脚分配。管脚分配完成后在Process状态栏中勾选Map Design下的Map Trace和Place & Route Design下的Place & Route Trace,双击Place & Route Design进行布局布线,通过以后勾选Export Files下的Bitstream File并双击Export Files生成BIT流文件。

到这里,一个工程的bit流文件已生成成功,在接下来的文章中,我会继续向大家介绍bit流文件的烧录以及工程IP核的添加、在线调试工具Reveal的使用,希望大家可以有所收获。