本文的文档编号:001400000010

需要看对应的视频,请点击视频编号:001400000088

1、介绍了MDY最常用的至简设计verilog代码模板,以及如何调用和使用该模板的方法

第七章 明德扬的设计模板

明德扬的模板包括VERILOG最常用的代码,利用这些模板,按照模板提示的步骤思考和填空,就能得到简洁、漂亮的代码。

明德扬模板有人认为只是节省敲代码时间,这是大错特错的。明德扬的模板更多地是将明德扬的设计经验转化到模板当中,不让设计者思想随意飘,保证按照规范的思路去设计。

|

命令 |

作用 |

|

Module |

可以调出verilog模块的模板。该模板已经包括模块的常用部分,在相应位置补充就非常方便地完成设计。 |

|

Shixu |

“时序”的拼音。可以调出时序逻辑的模板。时钟和复位信号绝大部分情况下都无须修改。 always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin end else begin end end |

|

Zuhe |

“组合”的拼音。可以调出组合逻辑的模板。 always @(*)begin end |

|

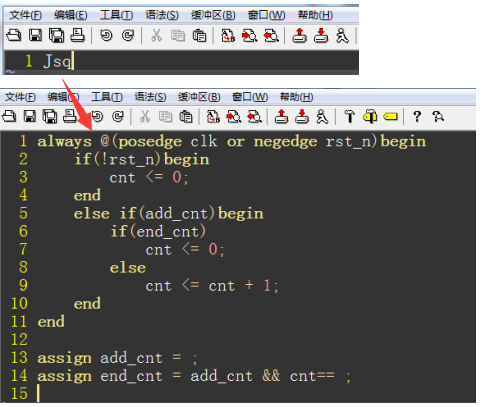

Jsq |

“计数器”拼音的缩写。可以调出明德扬计数器的模板。 |

|

Ztj |

“状态机”拼音的缩写。可以调出明德扬四步法状态机的模板。 |

|

Test |

可以调出测试文件的模板。 |

|

Regx |

定义reg信号时使用。其中x是指位宽数字,目前支持1,2,3,4,8,16,32。 当x为1时,即Reg1,可以调出以下语句: reg ; 当x为其他值时,如Reg8时,可以调出以下语句: reg [ 7: 0] ; |

|

Wirex |

定义wire信号时使用。其中x是指位宽数字,目前支持1,2,3,4,8,16,32。 当x为1时,即Wire1,可以调出以下语句: wire ; 当x为其他值时,如Wire8时,可以调出以下语句: wire [ 7: 0] ; |

|

Inputx |

定义input信号时使用。其中x是指位宽数字,目前支持1,2,3,4,8,16,32。 当x为1时,即Input1,可以调出以下语句: input ; 当x为其他值时,如Input8时,可以调出以下语句: input[ 7: 0] ; |

|

Outputx |

定义output信号时使用。其中x是指位宽数字,目前支持1,2,3,4,8,16,32。 当x为1时,即Output1,可以调出以下语句: output ; 当x为其他值时,如Output8时,可以调出以下语句: output[ 7: 0] ; |

|

Initial |

用于调用测试文件中initial段的语句。语句中补充了#1延时,请注意不要删除。 initial begin #1; end |

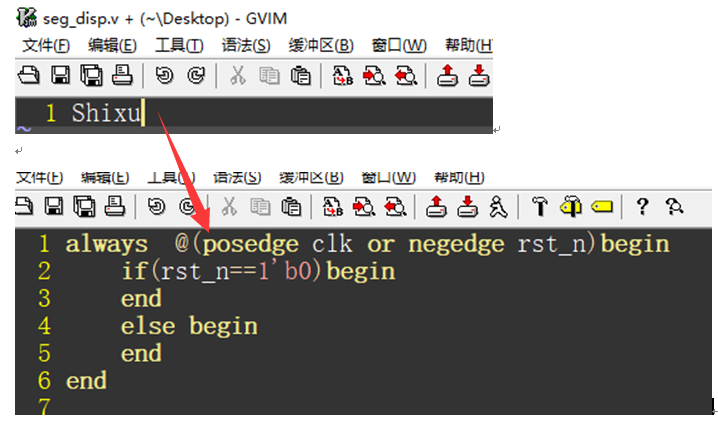

例1:输入Shixu,回车,得到最常用的时序ALWAYS模板。时钟和复位信号一般固定,只需要填写条件即可。

图 92

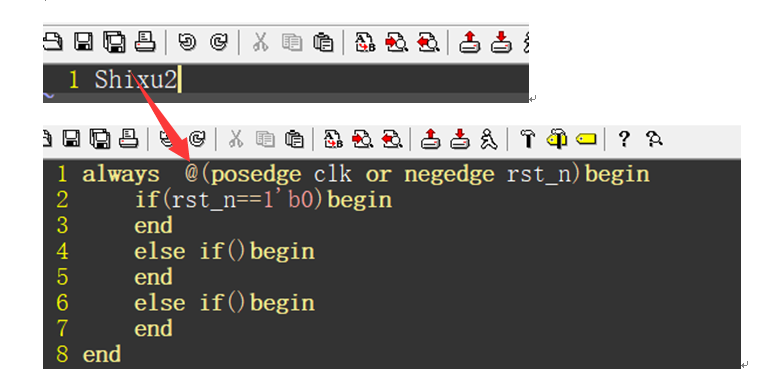

例2:输入Shixu2,回车,得到2个条件的时序ALWAYS模板

图 93

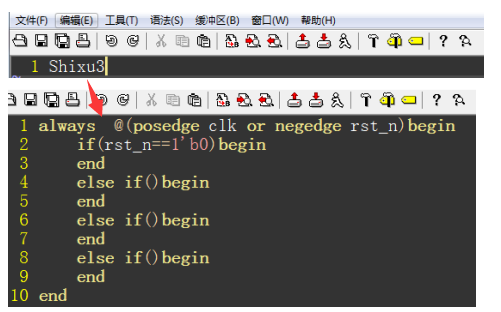

例3:输入Shixu3,回车,得到3个条件的时序ALWAYS模板

图 94

例4:输入Jsq,回车,得到1个计数器模板

图 95

例5:输入Jsq2,回车,得到2个计数器模板

图 96

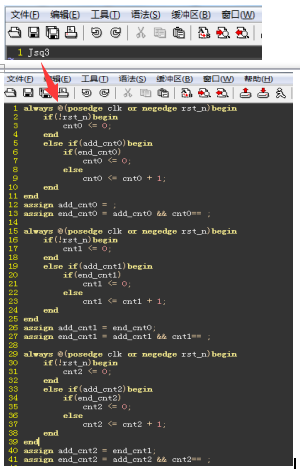

例6:输入Jsq3,回车,得到3个计数器模板

图 97

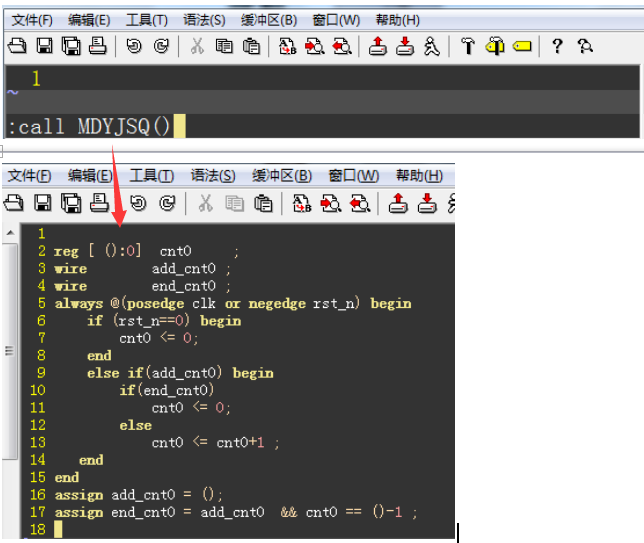

例7:命令模式下输入:call MDYJSQ(),回车,得到1个计数器模板

图 98

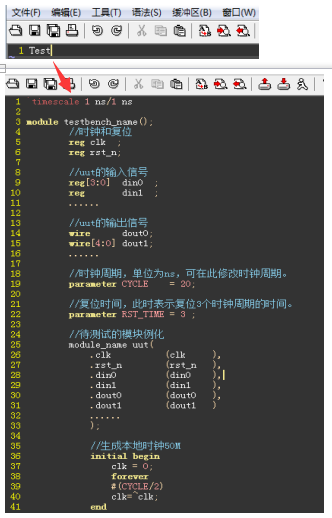

例8:输入Test,回车,得到测试文件模板

图 99

例9:输入Zuhe,回车,得到组合逻辑的always模板

图 100

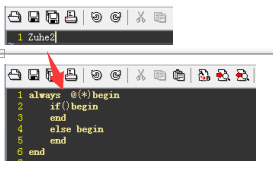

例10:输入Zuhe2,回车,得到有条件的组合逻辑的always模板。

图 101

例11:输入Module,回车,得到模块设计的模板

图 102

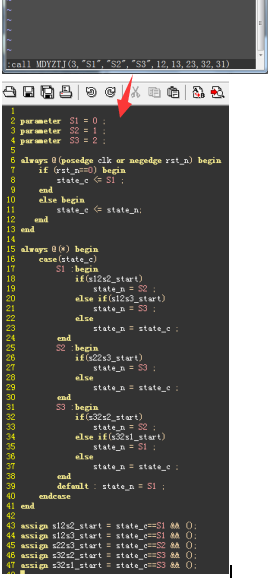

例12:命令模式下输入:call MDYZTJ(3,”S1”,”S2”,”S3”,12,13,23,32,31),回车,得到3个状态机相应跳转的模板

图 103

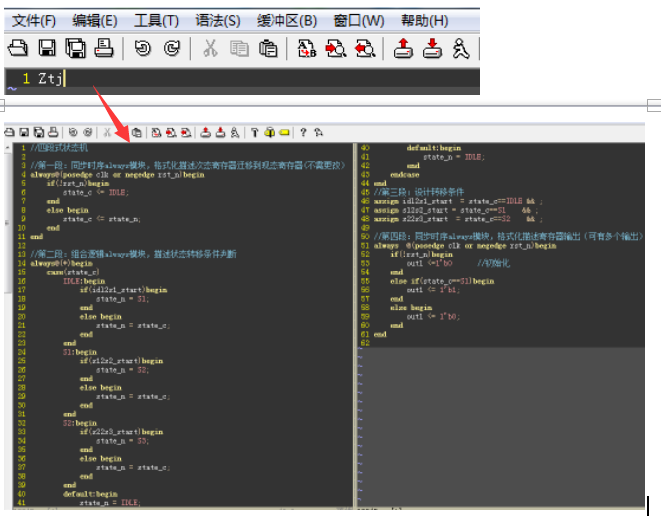

例13:输入Ztj,回车,得到状态机的模板

图 104

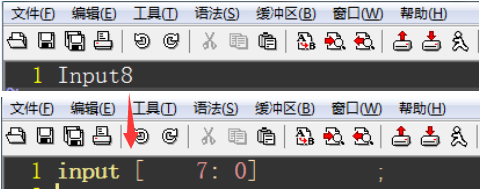

例14:输入Input8,回车,得到输入信号位宽为8的模板

图 105

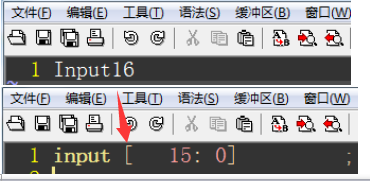

例15:输入Input8,回车,得到输入信号位宽为16的模板

图 106

例16:输入Wire32,回车,得到wire类型信号位宽为32的模板

图 107

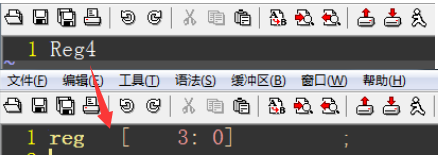

例17:输入Reg4,回车,得到reg类型信号位宽为4的模板

图 108

例18:输入Output16,回车,得到输出信号位宽为16的模板

图 109

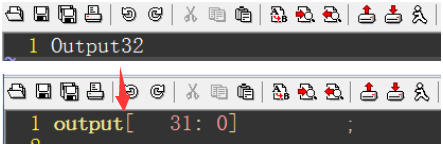

例19:输入Output32,回车,得到输出信号位宽为32的模板

图 110

提醒:要获取以上模板,则需要安装明德扬提供的GVIM软件,并且按照提示正确安装。该工具的下载链接请找客服人员。