|

需要看对应的视频,请点击视频编号:001100000057 1、本视频主要介绍数字电路的高阻态,即Z态,表示设计者不驱动这个信号(既不给0也不给1),通常用于三态门接口当中

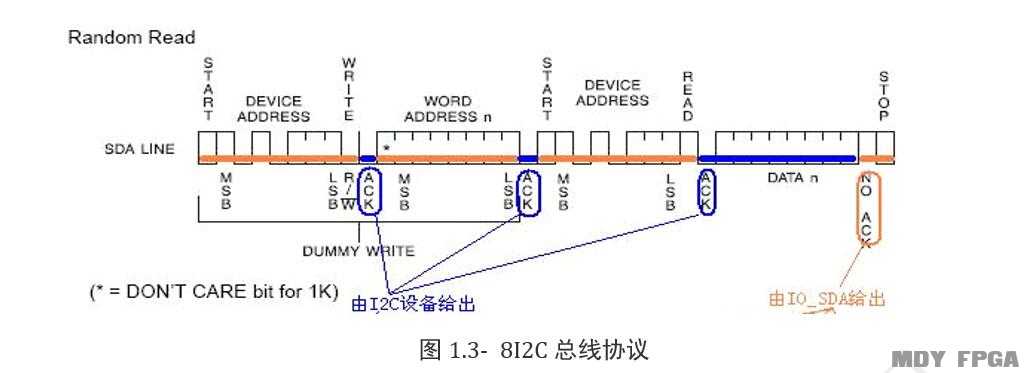

2、本视频通过I2C总线协议来说明三态信号的运用。

Z态,一般称之为高阻态,表示设计者不驱动这个信号(既不给0也不给1),通常用于三态门接口当中。

上图就是三态总线的应用案例,图中的连接总线对于CPU和FPGA来说既为输入又为输出,是双向接口。 一般的硬件电路中会将该线接上一个上拉电阻(弱上拉)或下拉电阻(弱下拉)。 当CPU和FPGA都不驱动该总线时,A点保持为高电平。当FPGA不驱动该总线,CPU驱动该总线时,A点的值就由CPU决定。 当CPU不驱动该总线,FPGA驱动该总线时,A点的值就由FPGA决定。但FPGA和CPU不能同时驱动该总线, 否则A的电平就不确定了,通常FPGA和CPU何时驱动总线是按事先协商的协议进行工作。

上图是典型的I2C的时序。I2C的总线SDA就是一个三态信号。I2C协议已规定好上面的时间中, 哪段时间是由主设备驱动,哪段时间是由从设备驱动,双方都要遵守协议,不能存在同时驱动的情况。 那么FPGA在设计中是如何做到“不驱动”这一行为呢?这是因为FPGA内部有三态门。

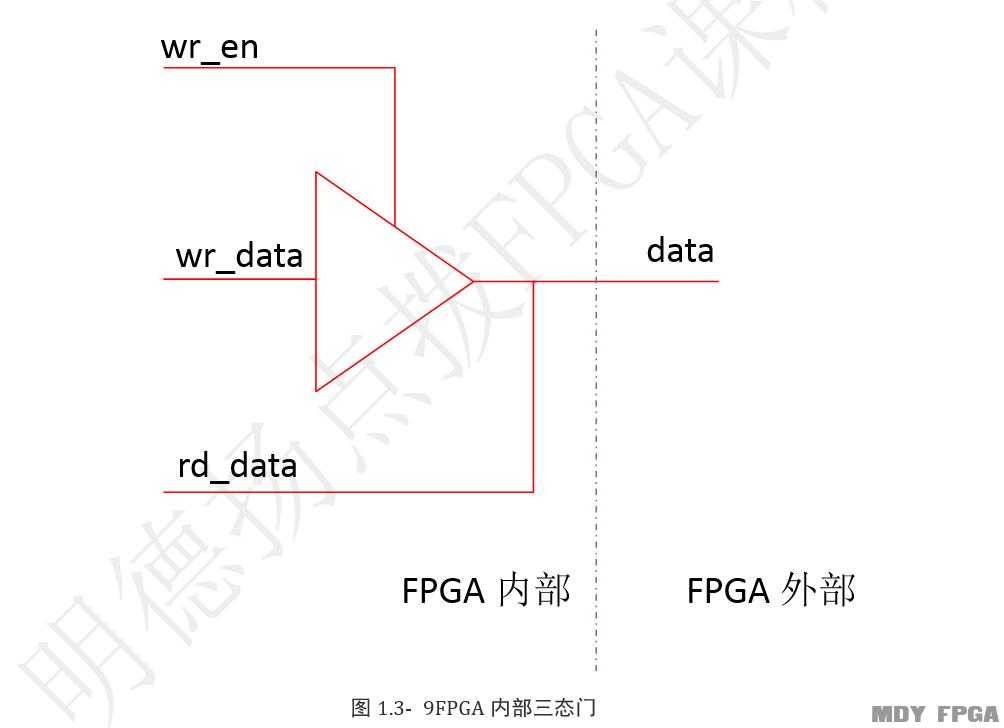

三态门是一个硬件,上图是它的典型结构。三态门有四个接口, 如上图所示的写使能wr_en、写数据wr_data、读数据rd_data以及与外面器件相连的三态信号data。 需要注意的是写使能信号,当该信号有效时三态门会将wr_data的值赋给三态线data,此时data的值由wr_data决定, 当wr_data为0时data值为0;当wr_data为1时data值为1。而当写使能信号无效时, 则不论wr_data值是多少都不会对外面的data值有影响,也就是不驱动。

在Verilog中以上功能是通过如下代码实现的:

当综合器看到这两行代码则知道要综合成三态门了,高阻z的作用正在于此。 此外可以注意到硬件上用三态线是为了减少管脚,而在FPGA内部没有必要减少连线, 所以使用三态信号是没有意义的。因此,笔者建议各位读者在进行设计时不要在FPGA内部使用高阻态“z”, 因为没有必要给自己添加“思考”的麻烦。当然,如果设计中使用了高阻态也不会报错,也可以实现功能。

总的来说高阻态“z”是表示“不驱动总线”这个行为,实际上数字电路就是高电平或者低电平,

不存在其他电平的情况。 相关视频:https://www.bilibili.com/video/BV1yf4y1R7gH?p=11

|