|

本节的文档编号:001100000061

需要看对应的视频,请点击视频编号:001100000058

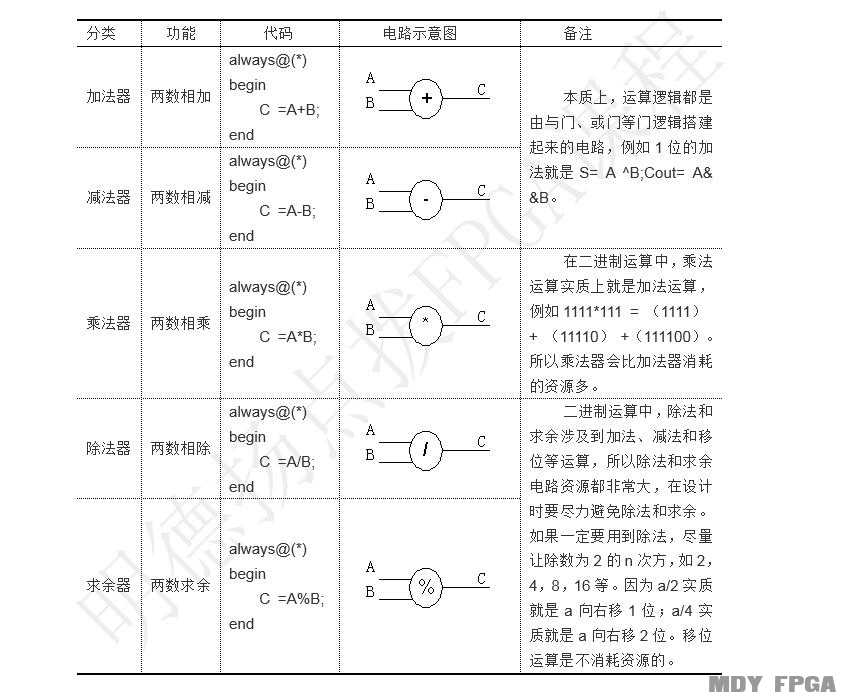

1、本节主要进行组合逻辑的介绍,包括:程序语句(assign语句、always语句),数字进制(二进制、不定态、高阻态),算数运算符(加、减、乘、除运算符),逻辑运算符(逻辑与、或、非运算符),按位逻辑运算符(单目按位与、或、非运算符,双目按位与、或、异或运算符),关系运算符,移位运算符(左移、右移运算符),条件运算符(三目运算符、if语句、case语句、选择语句等),拼接运算符;

5.3 算术运算符

算术运算符包括加法“+”、减法“-”、乘法“*”、除法“/”和求余“%”, 其中常用的算术运算符主要有:加法“+”,减法“-”和乘法“*”。 注意,常用的运算中不包括除法和求余运算符,这是由于除法和求余不是简单的门逻辑搭建起来的, 其所对应的硬件电路比较大。 加减是最简单的运算,而乘法可以拆解成多个加法运算,因此加减法、乘法所对应的电路都比较小。 而除法就不同了,同学们可以回想一下除法的步骤,其涉及到多次乘法、移位、加减法, 所以除法对应的电路是复杂的, 这也同时要求设计师在进行Verilog设计时要慎用除法。

5.3.1加法运算符

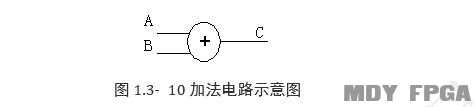

首先学习加法运算符,在Verilog代码中可以直接使用符号“+”:

其电路示意图如下所示:

综合器可以识别加法运算符并将其转成如上图所示的电路。二进制的加法运算和十进制的加法相似, 十进制是逢十进一,而二进制是逢二进一。

二进制加法的基本运算如下:

0 + 0 = 0;

0 + 1 = 1;

1 + 0 = 1;

1 + 1 = 10;

两位的二进制加法

11 + 1 = 100;

11 + 11 = 110;

…

5.3.2减法运算符 减法运算符,在Verilog代码中可以直接使用符号“-”:

其电路示意图如下所示:

综合器可以识别减法运算符并将其直接转成上图所示的电路。

二进制的减法运算和十进制的减法运算是相似的,也有借位的概念。十进制是借一当十,二进制则是借一当二。

1位减法基本运算如下:

0 - 0 = 0;

0 - 1 = 1,同时需要借位;

1 - 0 = 1;

1 - 1 = 0 ;

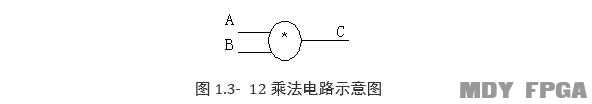

5.3.3乘法运算符 乘法运算符,在Verilog代码中可以直接使用符号“*”:

其电路示意图如下所示:

综合器可以识别乘法运算符,将其直接转成上图所示的电路。二进制的乘法运算和十进制的乘法运算是相似的, 其计算过程是相同的。

1位乘法基本运算如下:

0 * 0 = 0;

0 * 1 = 0;

1 * 0 = 0;

1 * 1 = 1;

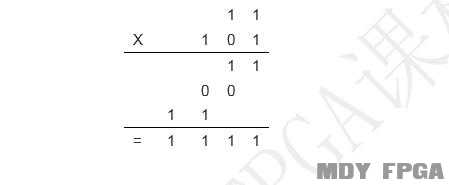

多位数之间相乘,与十进制计算过程也是相同的。

例如2’b11* 3’b101的计算过程如下:

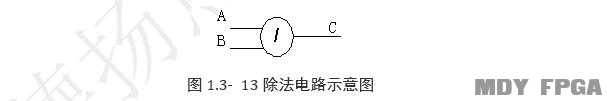

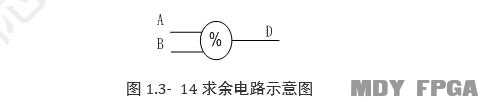

除法运算符,可以在Verilog代码中直接使用符号“/”,而求余运算符是“%”:

除法的电路示意图如下所示:

求余的电路示意图如下所示:

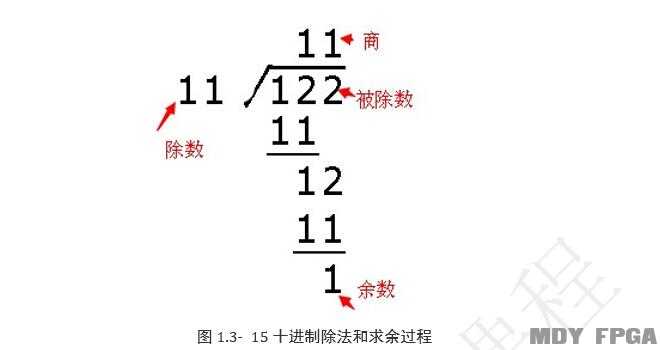

综合器可以识别除法运算符和求余运算符,但是这两种运算符包括大量的乘法、加法和减法操作, 所以在FPGA里除法器的电路是非常大的, 综合器可能无法直接转成上图所示的电路。 有读者可能会有疑问:为什么除法和求余会占用大量的资源呢? 可以来分析一下十进制除法和求余的过程,以122除以11为例。

在做上面运算的过程中涉及到多次的移位、乘法、减法等运算。 也就是说进行一次除法运算使用到了多个乘法器、减法器,需要比较大的硬件资源, 二进制运算也是同样的道理。 所以,在设计代码中,一般不使用除法和求余。在算法中会想各种办法来避免除法和求余操作。 因此在数字信号处理、通信、图像处理中会发现有大量的乘法、加减法等,却很少看到除法和求余运算。 但在仿真测试中是可以使用除法和求余的, 因为其只是用于仿真测试而不用综合成电路,自然也就不需要关心占用多少资源了。

相关视频:https://www.bilibili.com/video/BV1yf4y1R7gH?p=12 |