边缘检测工程:Ascii转十六进制模块代码解析

作者:小黑同学

本文为明德扬原创文章,转载请注明出处!

Ascii转十六进制模块的功能:将ASCII所对应的16进制数,转成实质的16进制数。

一、设计架构

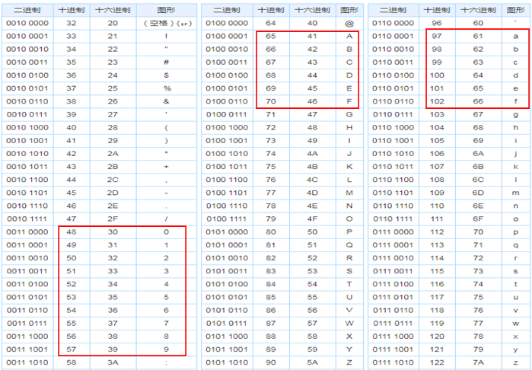

上图是Ascii码表对应的数据。我们从图中可以获取到如下关键信息。

1. Ascii码0~9对应的十六进制数为8’h30~8’h39,也就是说收到ASCII码的16进制数8’h30~8’h39时,就转成0~9,也就是减去8’h30。

2. Ascii码A~F对应的十六进制数为8’h41~8’h46,也就是说收到ASCII码的16进制数8’h41~8’h46时,就转成A~F,也就是减去8’h37。

3. Ascii码a~f对应的十六进制数为8’h61~8’h66,也就是说收到ASCII码的16进制数8’h61~8’h66时,就转成a~f,也就是减去8’h57。

本模块的功能,是对ASCII码的0~9,a~f,A~F进行转换,其他数据不转换,不在此范围的,数据无效。例如:

当din=8’h31(字符1),且din_vld = 1,则dout=4’h1,dout_vld=1;

当din=8’h41(大写字母A)时,且din_vld=1,则dout=4‘d10,dout_vld=1;

如果输入的ASCII不在数字0~9,A~F,a~f的时候,dout_vld就输出0。

当din=8’h49(大写字母I)时,且din_vld=1,则dout=0,dout_vld=0。

二、信号的意义

|

信号 |

类型 |

意义 |

|

clk |

输入信号 |

时钟信号。 |

|

rst_n |

输入信号 |

复位信号,低电平有效。 |

|

din |

输入信号 |

接收的Ascii码数据,位宽为8bit。 |

|

din_vld |

输入信号 |

输入数据有效指示信号,1bit位宽,当其为高电平时,对应输入数据有效,表示接收到一字节的数据。注意,一个时钟的高电平表示接收到一字节数据。 |

|

dout |

输出信号 |

Ascii码转化为十六进制数之后的输出,位宽为4bit。 |

|

dout_vld |

输出信号 |

输出数据有效指示信号,1bit位宽,当输入在红框范围内时,dout_vld为高电平,表示Ascii转十六进制转化成功,当输入不再红框范围内时,则dout_vld为低电平,表示数据无效。 |

三、参考代码

下面展出本模块的设计,欢迎进一步交流,如果需要源代码,欢迎与本人联系。

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61 |

module acsii2hex(

clk ,

rst_n ,

din ,

din_vld ,

dout ,

dout_vld

);

parameter DIN_W = 8;

parameter DOUT_W = 4;

input clk ;

input rst_n ;

input [DIN_W-1:0] din ;

input din_vld ;

wire [DIN_W-1:0] din ;

wire din_vld ;

output[DOUT_W-1:0] dout ;

output dout_vld ;

reg [DOUT_W-1:0] dout ;

reg dout_vld ;

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

dout_vld <= 0;

end

else if(din_vld&&((din>=8'd48&&din<8'd58)||(din>=8'd65&&din<8'd71)||(din>=8'd97&&din<8'd103)))begin

dout_vld <= 1;

end

else begin

dout_vld <= 0;

end

end

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

dout <= 0;

end

else if(din>=8'd48&&din<8'd58) begin

dout <= din - 8'd48;

end

else if(din>=8'd65&&din<8'd71) begin

dout <= din - 8'd55;

end

else if(din>=8'd97&&din<8'd103) begin

dout <= din - 8'd87;

end

else begin

dout <= 0;

end

end

endmodule |

明德扬专注FPGA研究,我司正在连载两本书籍:《基于FPGA至简设计法实现的图像边缘检测系统》(http://www.fpgabbs.cn/forum.php?mod=viewthread&tid=691)、《ASIC和FPGA时序约束理论与应用》(http://www.fpgabbs.cn/forum.php?mod=viewthread&tid=705),有兴趣点击观看。

也欢迎加入群(838209674),及时获取最新的文章信息,整个边缘检测工程源代码可加Q:1817866119(N老师)获取!