承接内容一:

4.考虑是否涉及指令系统

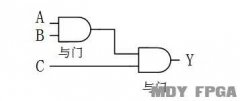

本项目涉及指令系统,上位机需要发送指令给FPGA,进而配置温度传感器,配置温度报警上限和下限值,同时可以发送指令控制数码管显示关闭,蜂鸣器开关。 因此,系统框图中需要加入“寄存器解析模块”,如下图所示:

5.考虑外围器件是否涉及寄存器配置

本项目中,DS18B20需要配置内部寄存器,但是本项目并没有采用MDY模板的方式(读取配置寄存器表的方式来对DS18B20进行配置),而是通过上位机发送配置命令,解析配置寄存器值再对DS18B20进行配置。

6.根据实际情况,增加、补充或者拆分独立对应模块,随时调整

到第6步,根据数据流向,需要对模块间的接口进行详细分析了,补充模块或者将功能相同的模块合并。

首先,从串口接口方向思考,

a) 接收到的数据是上位机发来的ASCII码,为了方便FPGA对指令解析,需要将ASCII码译码,转化为对应的十六进制。因此需要一个ASCII码转8bit十六进制模块;

b) 接下来,需要对接收包文的包头进行检测,符合正确包头条件的包文保留,否则丢包处理。所以需要一个包头检测模块,用来过滤接收到的有效包文;

c) 经过寄存器解析模块后,会将指令解析出来,根据指令功能要求可能分别发送给DS18B20、数码管显示开关控制模块、数码管段选位选接口模块、蜂鸣器控制接口模块;

d) 寄存器解析模块发送过来的是8bit数据,不能直接发送给DS18B20(18B20只接收单bit),所以在寄存器解析模块和单总线转换接口模块之间需要一个8bit转换为1bit模块;

e) 温度报警功能需要做判断实时温度是否大于上限值,是否小于下限值。所以需要一个实时温度值比较判断模块;

f) 然后,从DS18B20方向思考;

g) 采集到的温度数据,通过单bit接口转换模块传给FPGA的是单bit数据,为了后面方便FPGA对数据进行处理,需要将1bit转换为8bit。所以需要一个1bit转8bit模块;

h) 8bit温度数据需要经过计算处理,因此需要一个数据处理模块;

i) 上位机只显示ASCII码格式数据,为实现温度值在上位机上能显示,需要将8bit温度值转换为ASCII码,所以需要一个8bit十六进制数据转换为ASCII码模块;

j) 经过数据处理后的结果是十六进制,而数码管显示的是BCD码,为了实现数码管上显示正确数据,因此需要一个十六进制转BCD码模块。

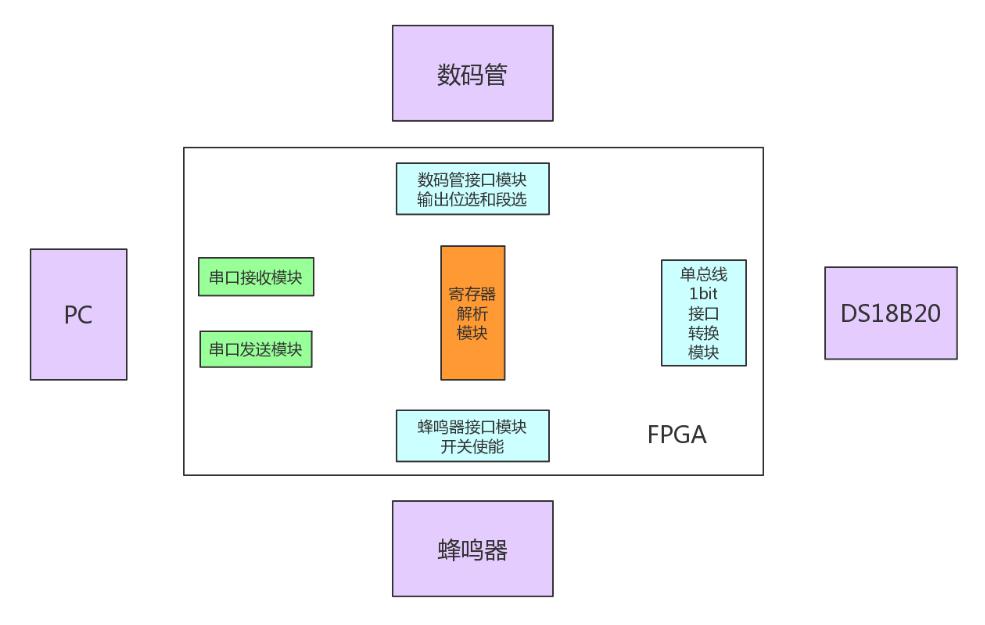

完善后如下图所示:

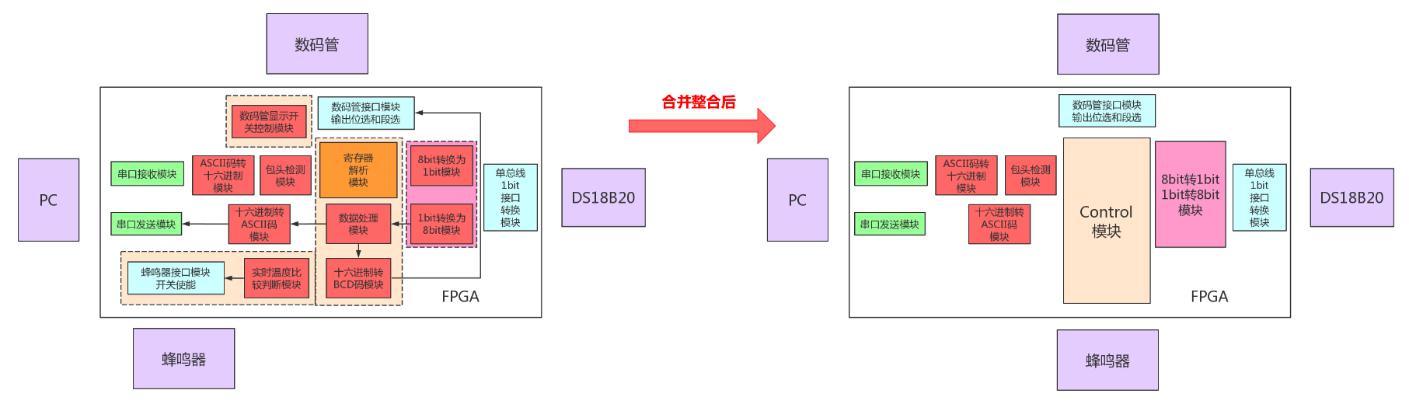

接下来将功能互斥、数据流向相关,接口一致的模块做合并化简处理,如下图所示:

7.考虑是否涉及多路进一路出,要用FIFO

本项目数据流方面没有涉及多路进一路出的问题,不需要考虑此处的FIFO问题。

8.考虑是否涉及到速率匹配问题,要加上RDY信号或者FIFO

本项目涉及速率匹配问题。

首先考虑与外围器件通信的接口上是否需要rdy信号。

与DS18B20通信是通过寄存器解析模块解析出对DS18B20的操作指令,发送给8bit转1bit模块,因此需要考虑DS18B20能否时刻响应操作指令?

这个问题在选择上位机与FPGA的通信接口时,已经考虑过了,串口的速率小于FPGA写DS18B20速率的。

查阅手册得知,写一次1bit的数据给18B20需要63us,8bit需要63*8=504us,小于串口发送一次8bit指令给FPGA时间1000000us/9600*8=833us。

所以串口接收数据通路上不需要考虑缓存FIFO问题。

在单总线1bit接口转换模块中,由于写DS18B20时序速率远小于FPGA内部读写频率,需要告知8bit转1bit模块每写1bit数据要等一等,待时序满足发送完1bit时序要求后,再发送新的1bit数据。所以在单bit接口转换模块与8bit转1bit模块间需要设rdy信号。

接下来考虑一下串口发送端。由于串口发送模块进行并串转换需要时间,因此串口发送模块需要告知上游十六制转ASCII码模块等一等,因此在串口发送模块与十六进制转ASCII码模块间需要设rdy信号。

由于串口发送模块并串转换需要等待,从而导致十六进制转ASCII码模块也需要缓存control模块发来的数据。因此十六进制转ASCII码模块中需要引入FIFO。

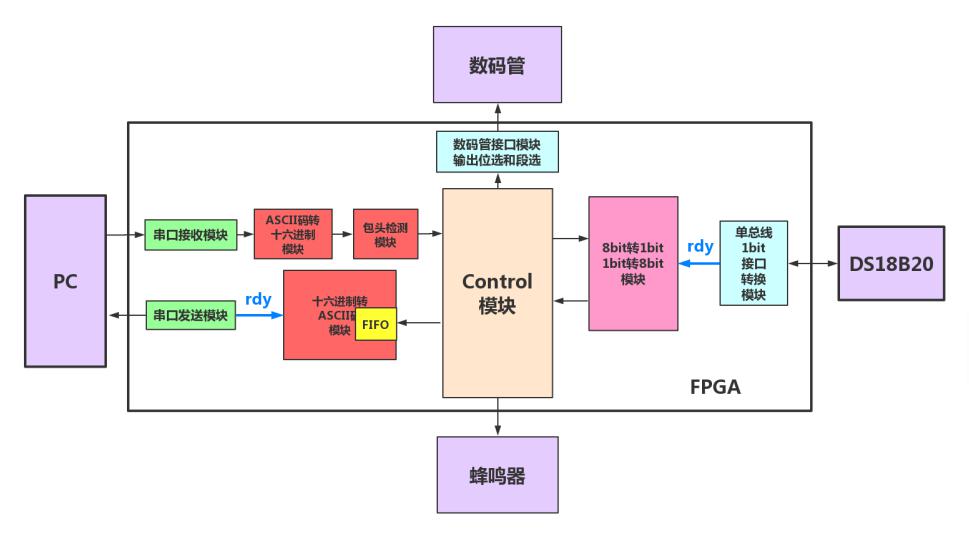

最终得到的模块图如下所示:

到此,根据模块划分步骤一步步做下来,温度检测工程的模块划分雏形初步已经完成。具体实践中需要根据FPGA内部信号的调整,随时拆分或独立来增减功能模块。

以上就是我做模块划分的基本思路,大家有什么问题可以加Q群544453837进行交流,更多FPGA相关资料可以登录明德扬论坛进行学习讨论:http://www.fpgabbs.cn/!