PCIE XDMA IP核介绍

本文为明德扬原创文章,转载请注明出处! 作者:云哥哥

1.PCIE的发送和接收数据

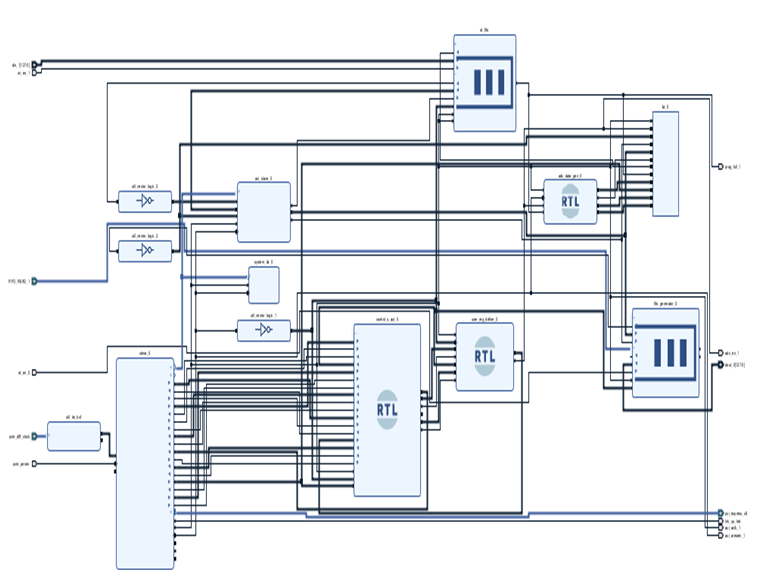

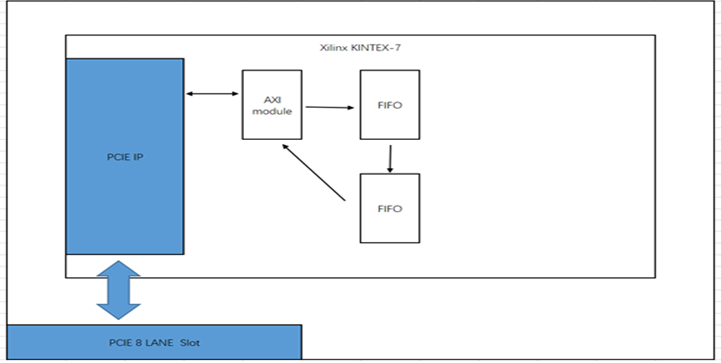

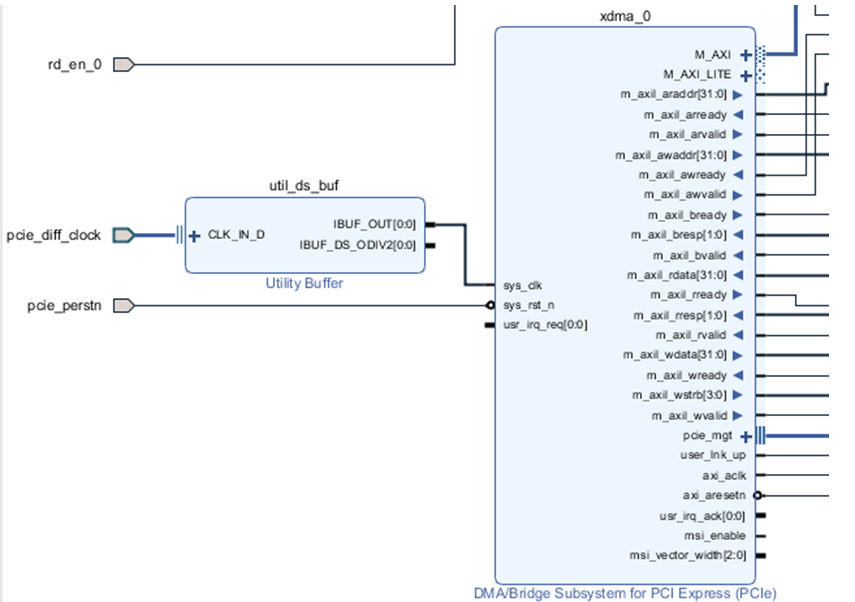

本工程的目的是在XC7K325tffg的平台上实现pcie的数据发送和接收,速率8通道2.5GB/s,首先看下本工程的PCIE部分的结构:

架构

各个模块的作用

PCIE部分结构图

这是PCIE IP核,主要用来发送数据,发送引擎主要负责将待发送数据按照PCIE协议组织成不同类型的TLP数据包,并发送给PCIE IP核;发送DMA控制模块主要负责把DDR3中读取的数据转换成TLP格式,并传送给发送引擎;接收引擎用于从PCIE IP核接收不同类型的TLP数据,接收DMA控制模块用于实现存储器读请求包的发送流量控制及接收数据位宽的转换;DMA状态控制寄存器模块主要用来解析来自PC对模块内部寄存器的命令和配置,并通知发送引擎模块、接收引擎模块及其他模块作出相应执行。

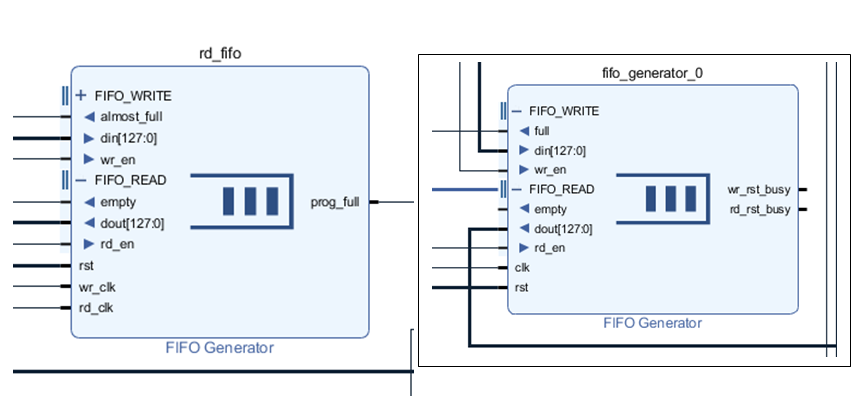

图表 SEQ 图表 \* ARABIC 1

图表一中 左图Rd_fifo是数据写入缓存模块,右图是读出缓存数据模块。

Fifo:先入先出队列。数字电路设计中所说的fifo实际是指fifo存储器,主要用于数据缓存和异步处理,fifo存储器缓存数据也遵循先入先出的原则。Fifo本质是一个RAM,它与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读写数据。

信号列表

|

名称 |

方向 |

位宽 |

说明 |

|

FIFO_read_1_empty |

o |

1 |

读fifo的空信号指示 1:读fifo里面没有数据 0:读fifo里面有数据 |

|

FIFO_READ_1_rd_data |

o |

128 |

读fifo数据的输出 |

|

FIFO_READ_1_rd_en |

i |

1 |

读fifo的使能 1:读出读fifo里面的数据 0:不读数据 |

|

adc_en_1 |

o |

1 |

接收到的寄存器使能 1:寄存器0x0收到数据为0x01 0:寄存器0x0收到数据为0x00 |

|

Axi_aclk_1 |

o |

1 |

PCIE 对外提供的用户时钟 |

|

axi_aresetn_1 |

o |

1 |

Pcie对外提供的复位 |

|

din_1 |

i |

128 |

用户侧想要发送的数据接口 |

|

Lnk_up_led |

o |

1 |

Pcie连接指示信号 |

|

Pci_express_x8_rxn |

i |

8 |

Pcie的接收管脚n端 |

|

Pci_express_x8_rxp |

i |

8 |

Pcie的接收管脚p端 |

|

Pci_express_x8_txn |

o |

8 |

Pcie的发送端n端 |

|

Pci_express_x8_txp |

o |

8 |

Pcie的发送端p端 |

|

pcie_diff_dock_clk_n |

i |

1 |

Pcie时钟信号n端 |

|

Pcie_diff_dock_clk_p |

i |

1 |

Pcie时钟信号p端 |

|

Pcie_perstn |

i |

1 |

Pcie得复位管脚 |

|

Prog_full_1 |

o |

1 |

写fifo的满信号 |

|

wr_en_1 |

i |

1 |

写fifo的写使能 |

以上就是pcie xdma ip核介绍,想要学习更多内容的同学,可以加Q:1465617980 云哥哥 了解更加专业的知识!