二、基本概念

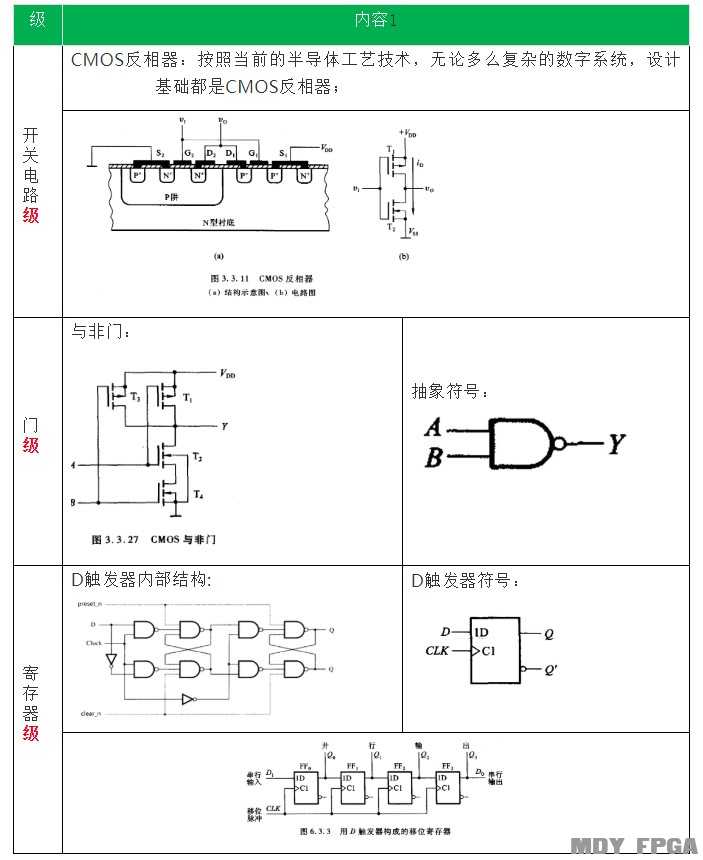

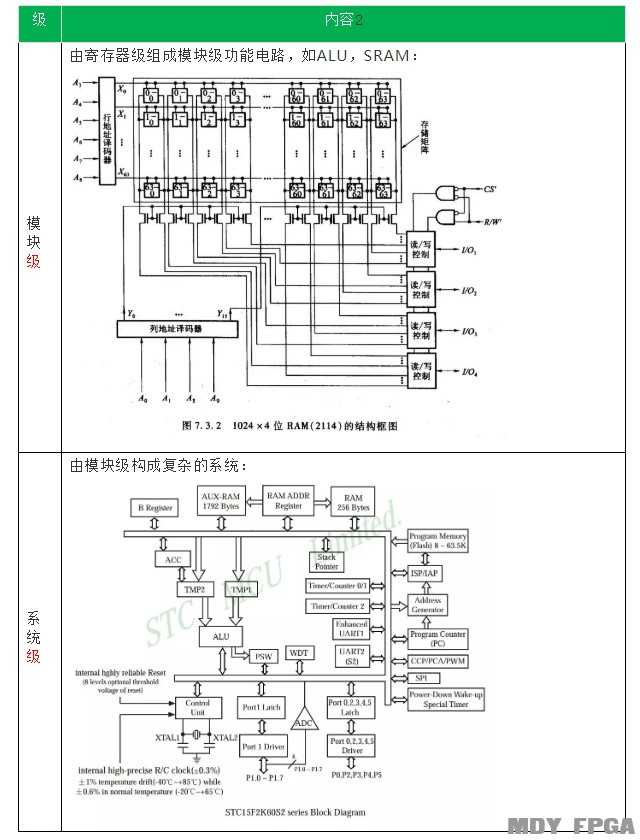

2.2硬件电路

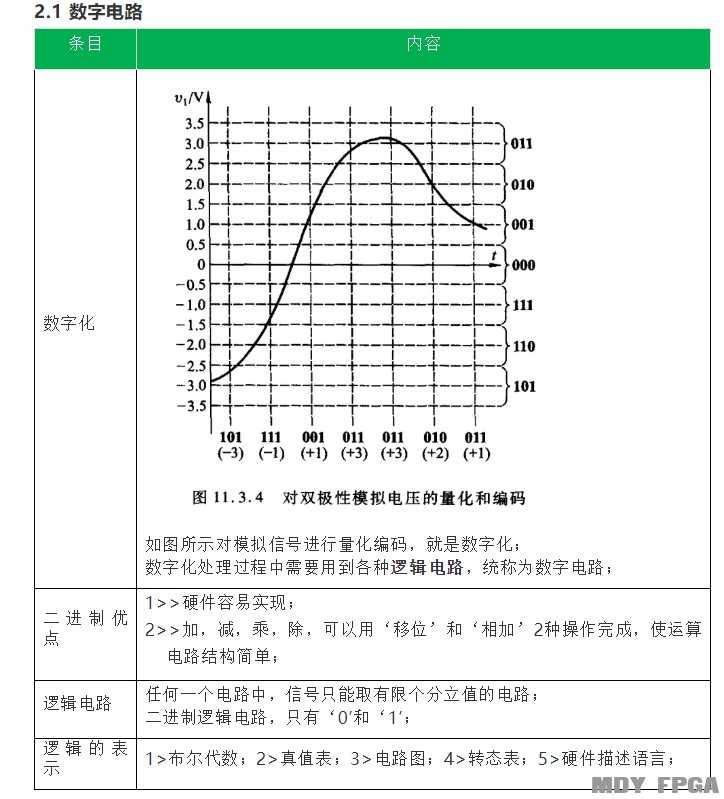

2.2 数制

2.2.1 进制转换表

2.3 编码

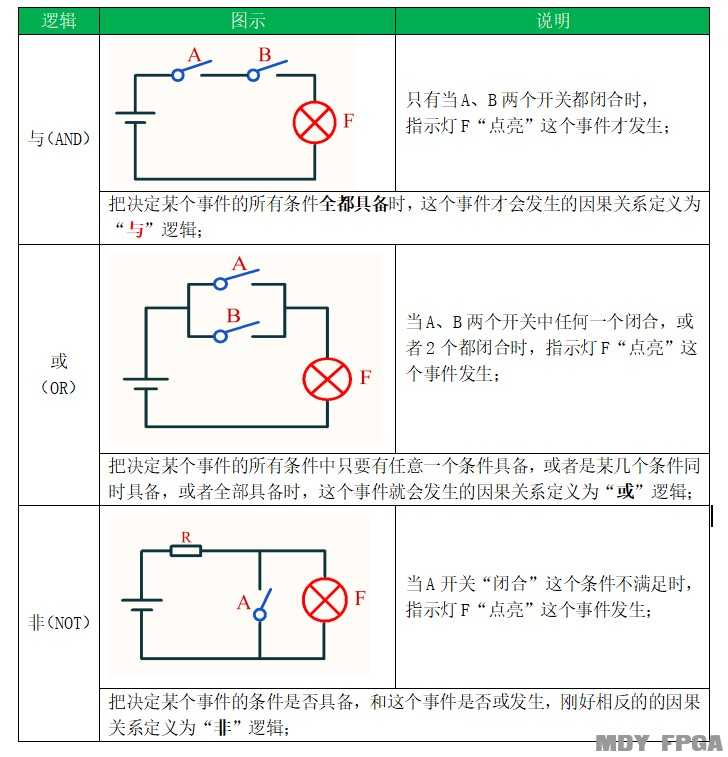

2.4 逻辑代数基础

2.4.1 布尔代数

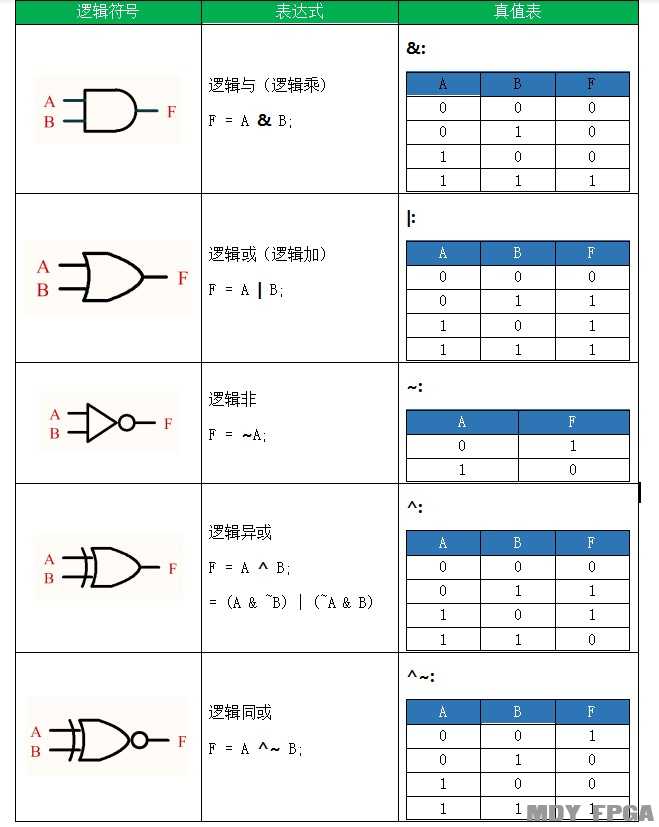

2.4.2 基本逻辑运算

2.4.3 基本逻辑表达

2.4.4 逻辑函数

2.5 电路分类

2.6 建模

2.6.1 建模概述

2.6.2 Verilog逻辑设计

三、 组合逻辑电路

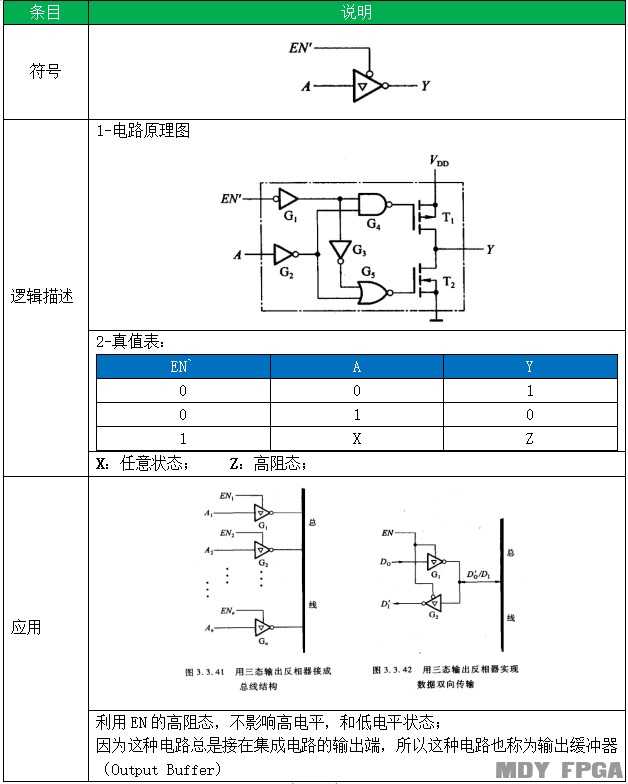

3.1 三态门3.1.1 工作原理

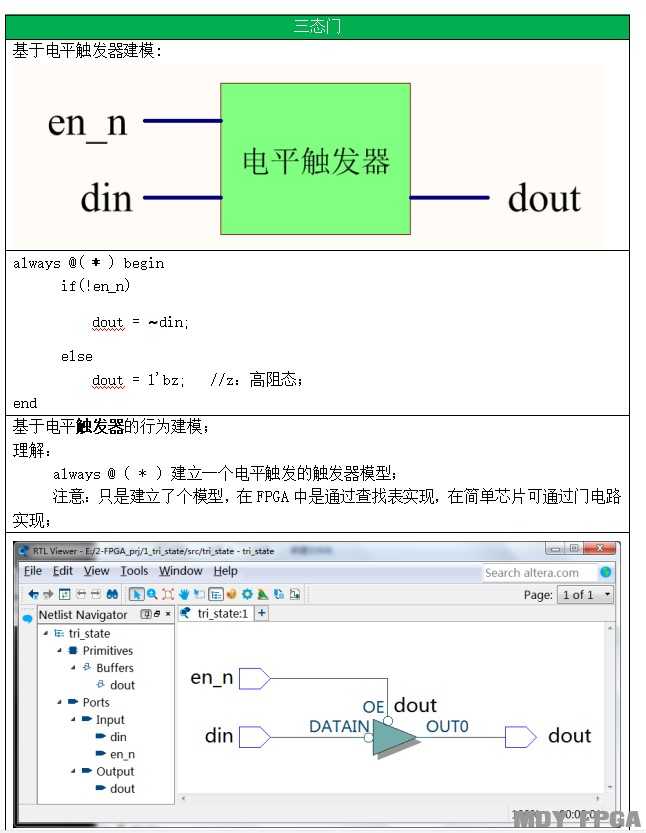

3.1.2 行为建模

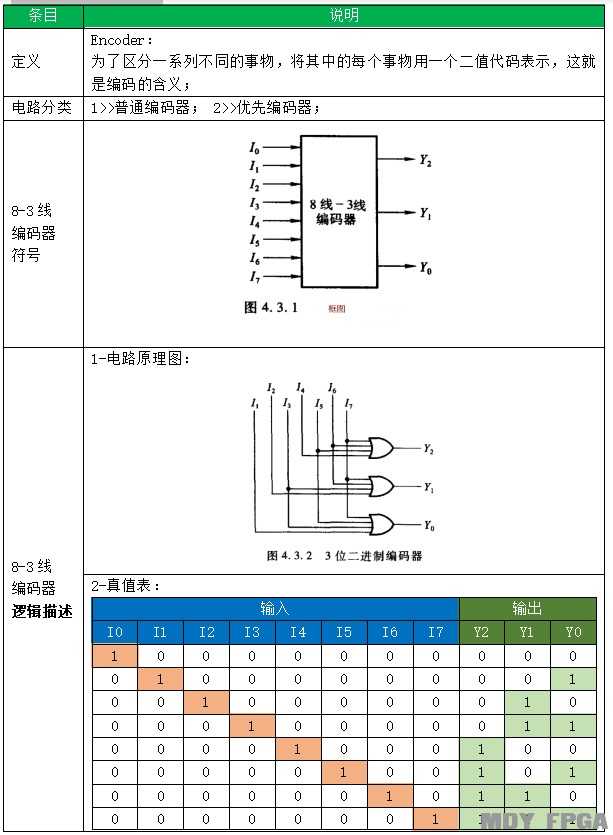

3.2 编码器

3.2.1 工作原理

3.2.2 行为建模

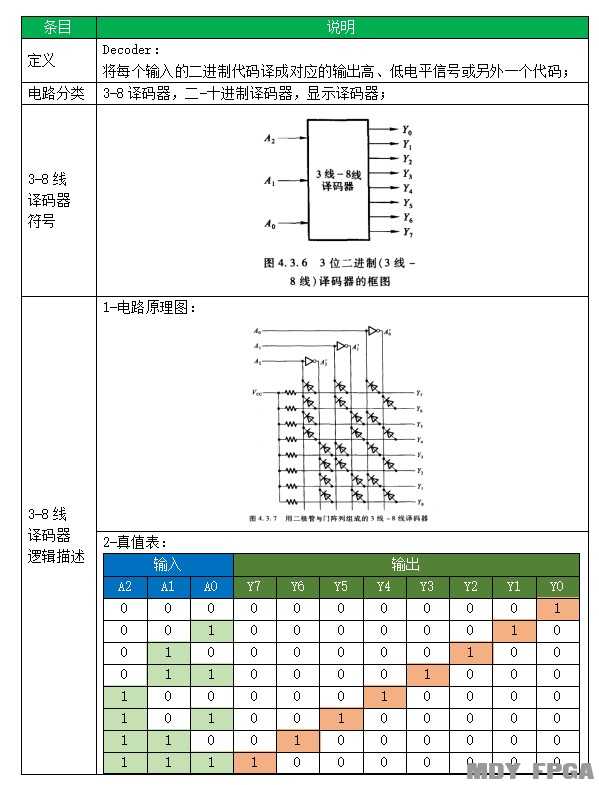

3.3 译码器

3.3.1 工作原理

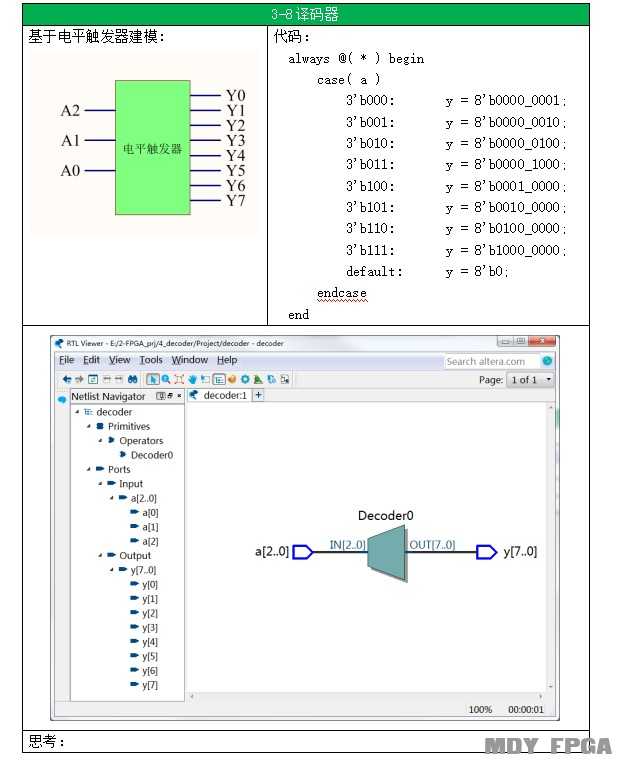

3.2.2 行为建模

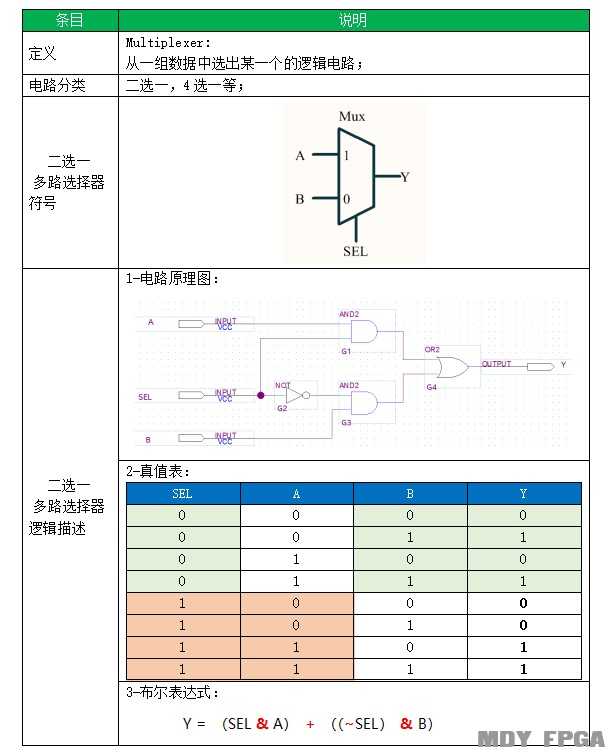

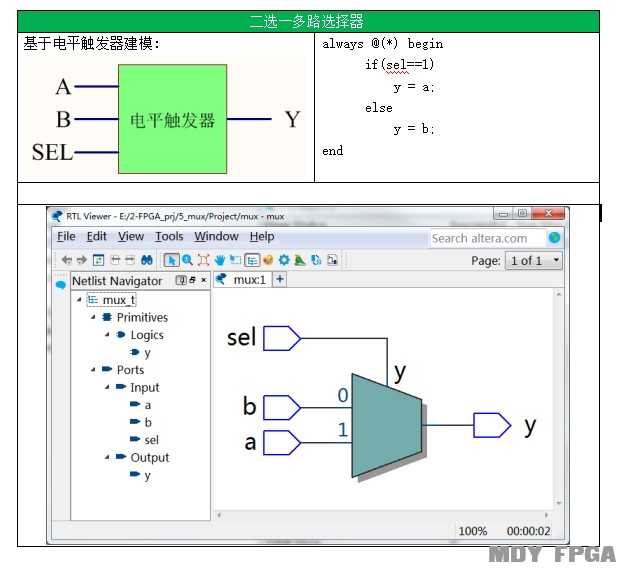

3.4 数据选择器

3.4.1 工作原理

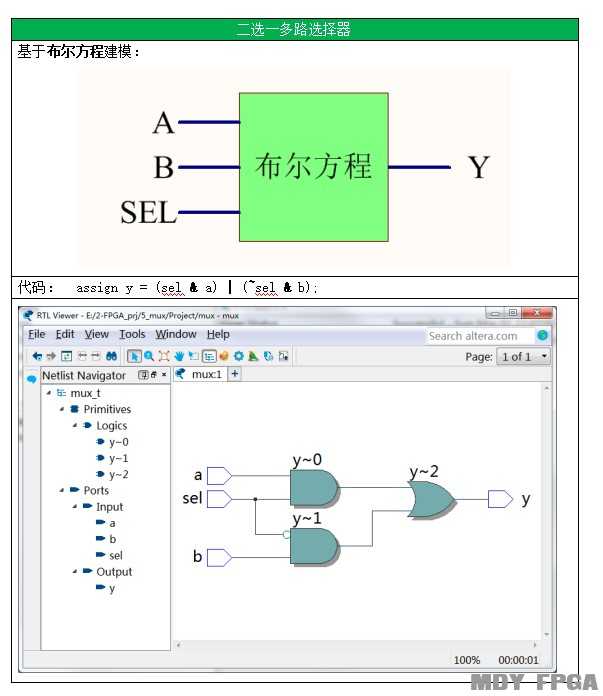

3.4.2 行为建模1

3.4.3 行为建模2

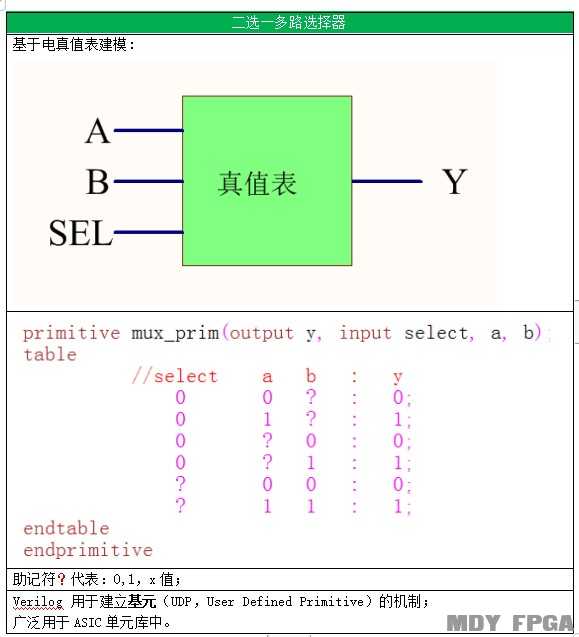

3.4.3 真值表建模

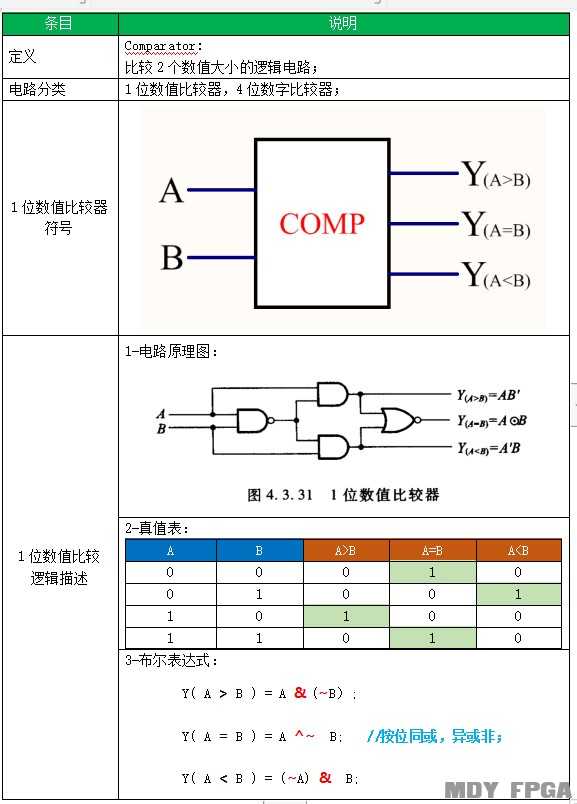

3.5.1 工作原理

3.5.2 行为建模1

3.5.2 行为建模2

四、 时序逻辑电路

4.1 概述

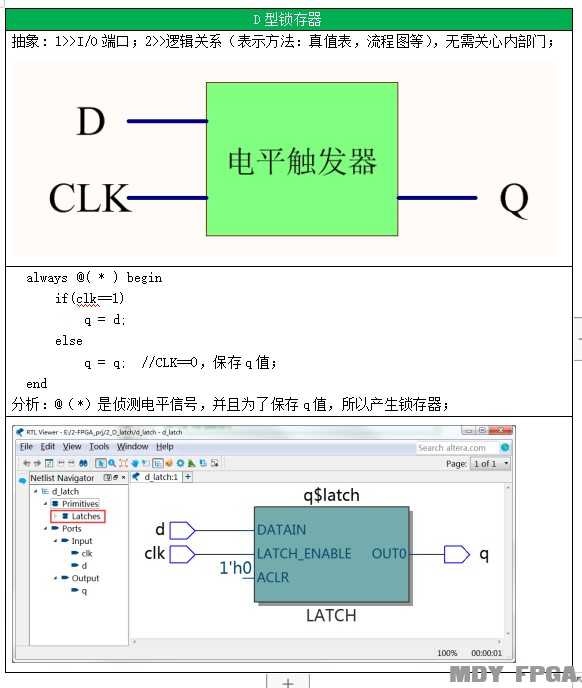

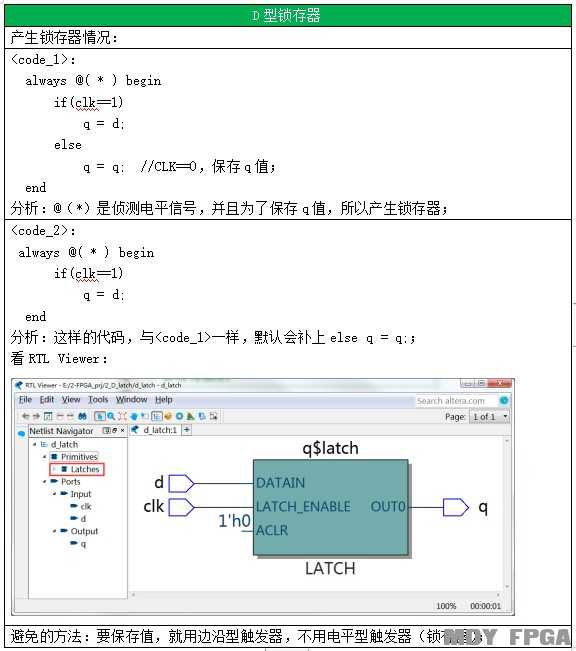

4.2 D型锁存器

4.2 D型锁存器

4.2.1 工作原理

4.2.2 行为建模

4.2.3 避免锁存器

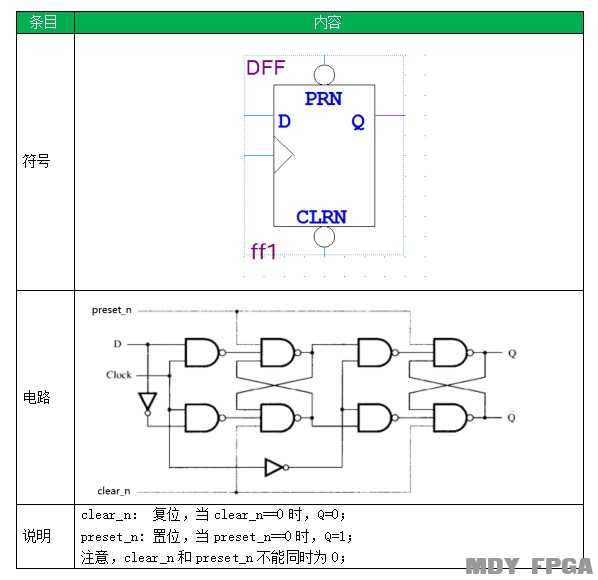

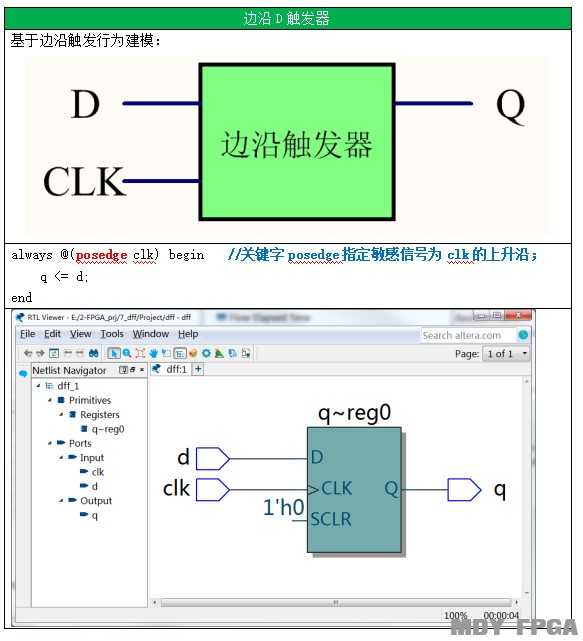

4.3.1 工作原理

4.3.2 复位/置位D型触器

4.3.3 行为建模

4.4 寄存器

4.4.1 工作原理

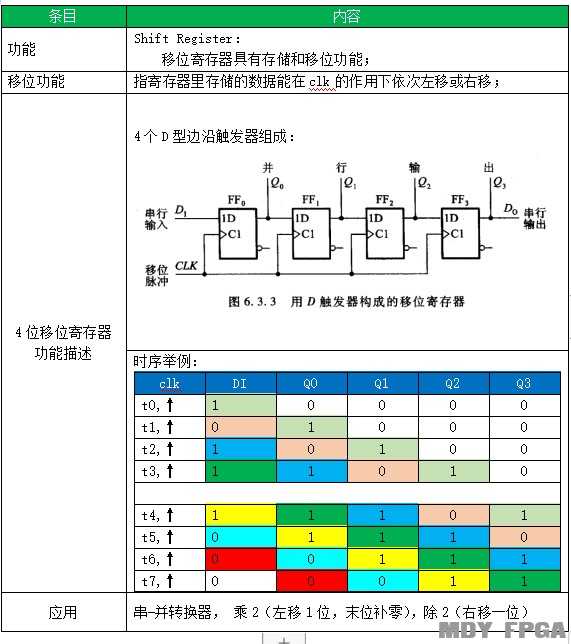

4.5 移位寄存器

4.5.1 工作原理

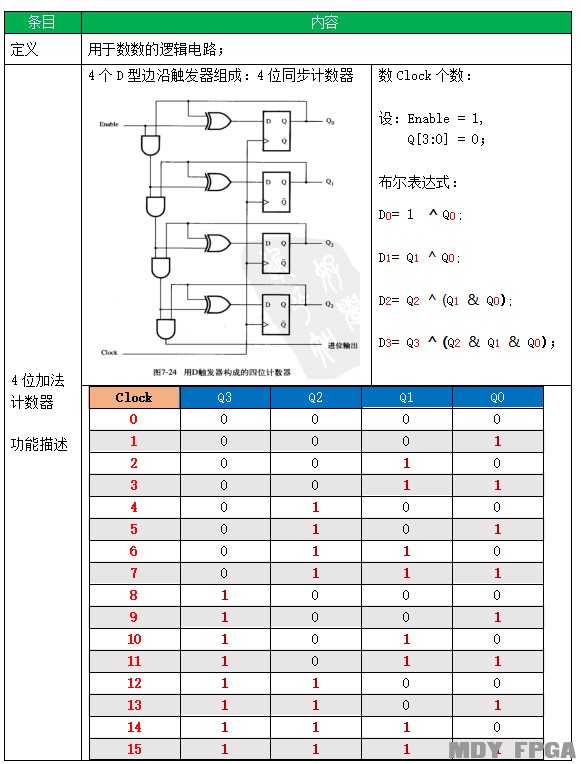

4.6 计数器

4.6.1 工作原理

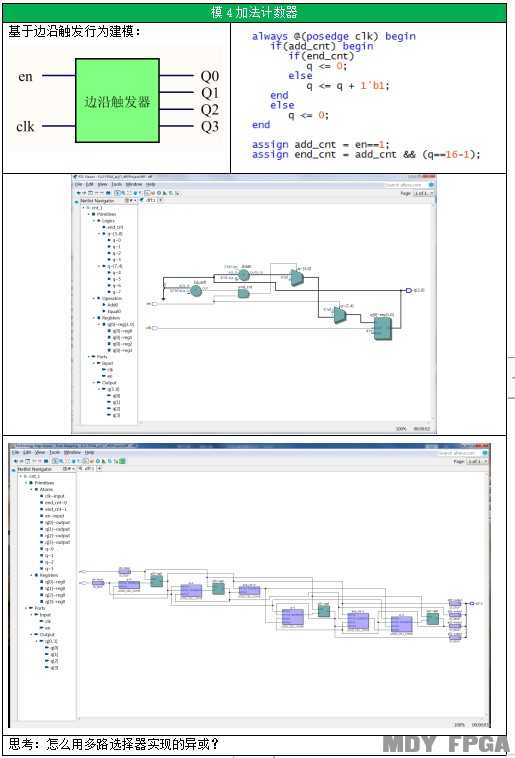

4.6.2 行为建模

4.6.3 时序分析

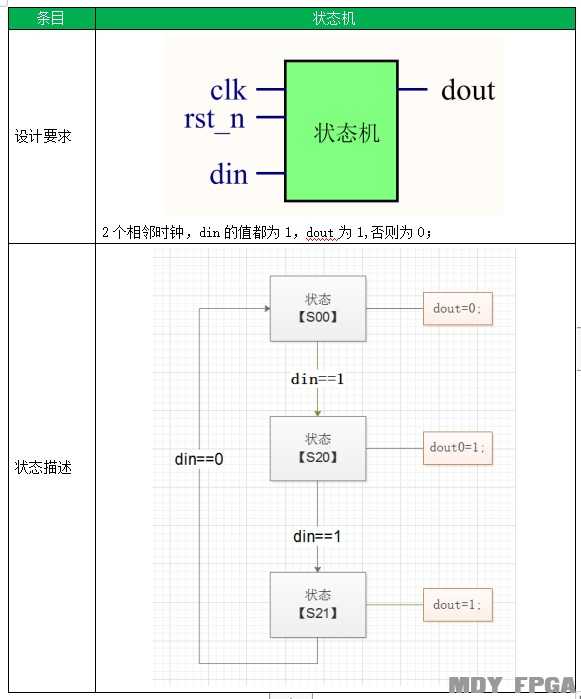

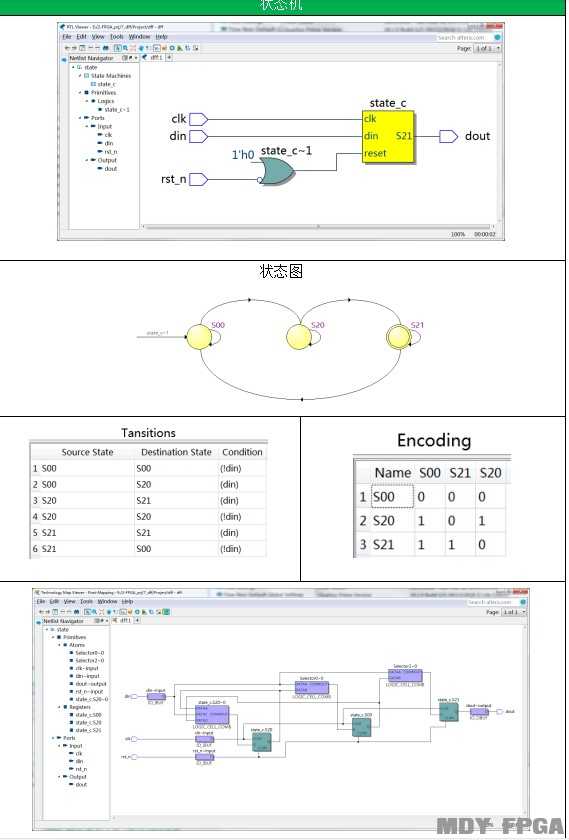

4.7 状态机

4.6.1 概述

4.6.2 SFC

4.6.3 状态机描述

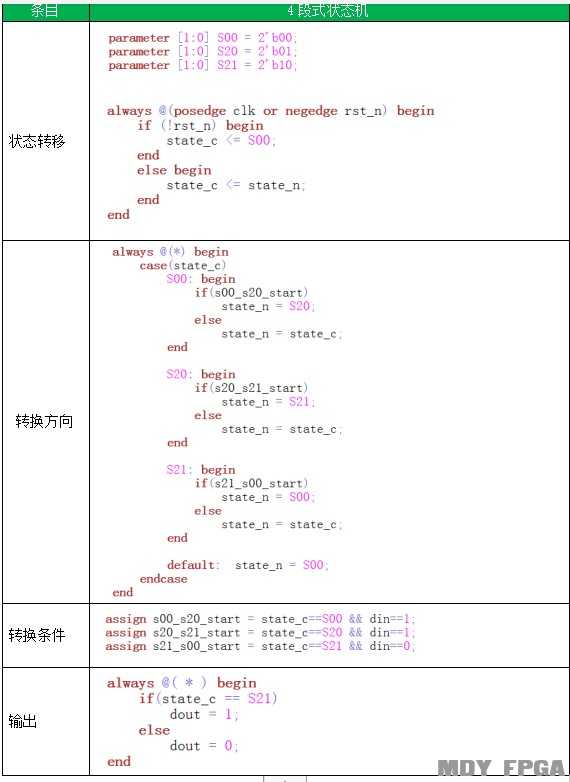

4.6.4 状态机实现

4.6.5 状态机图示

五、 算术运算电路

5.1 加法器

5.1.1 半加器工作原理

5.1.2 半加器行为建模

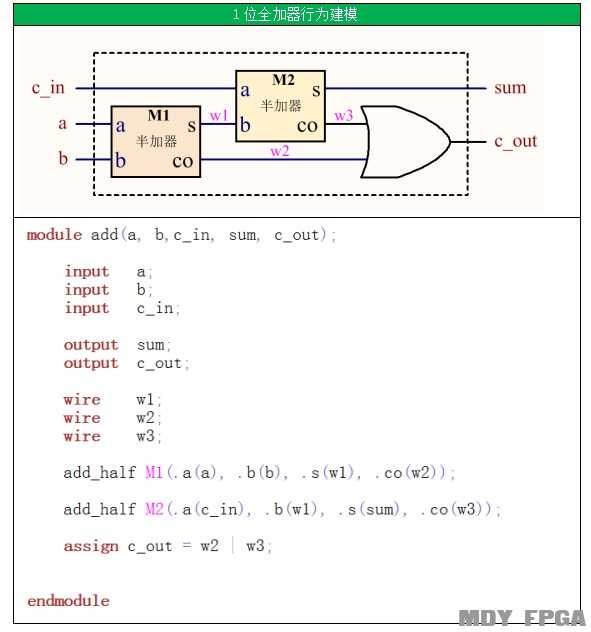

5.1.3 1位全加器工作原理

5.1.5 1位全加器行为建模

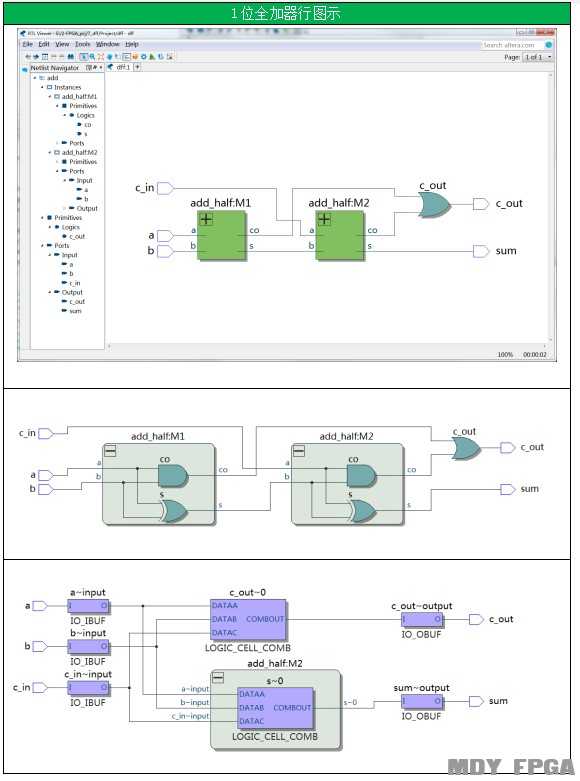

5.1.6 1位全加器行图示

5.2 减法器5.2.1 原码

5.2.1 补码

5.2.1 补码