本文简要描述了 MDY 千兆网工程仿真的过程。

千兆网模块使用了一个比较大的 IP 核,即三速以太网 IP 核,该 IP 核较大,涉及的功能较多,不能像之前那样添加 altera_mf.v 文件就行。那了方便起见,还是使用了传统的,通过 QUARTUS 调用 MODELSIM 的方式进行仿真。

希望学员能根据本案例,举一反三,掌握 QUARTUS 调用 MODELSIM 的方法。

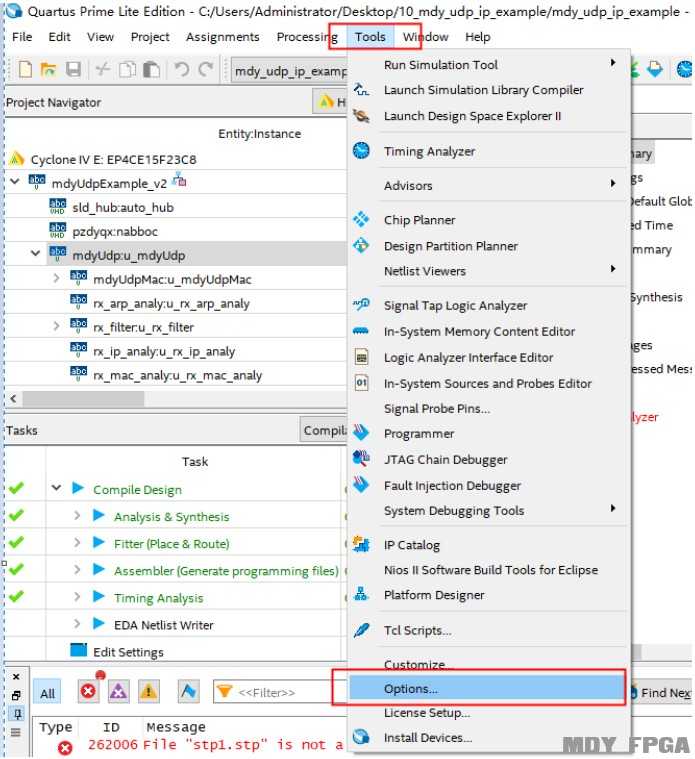

1. 设置 MODELSIM 工具路径

在 QUARTUS 中的 tools 栏中,点击 options 选项。

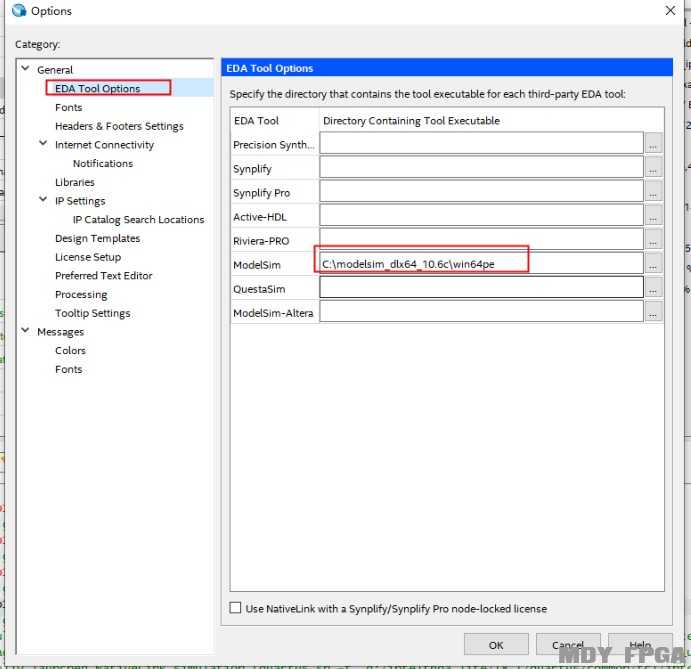

在弹出的窗口中,选择 EDA tool options,然后在 Modelsim 中选择 modelsim 的所在的路径。注意一般是在 win32 或者 win64pe 的目录。

2. 设置仿真文件

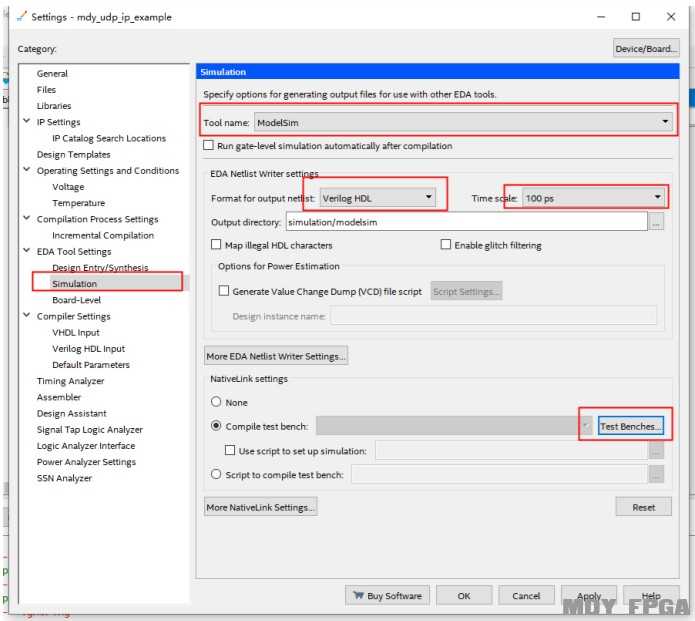

在工程的顶层文件中,右键选择 Settings。

在弹出的窗口中,先选择 Simulation。

在 Tool name 中,选择 Modelsim。(如果您的工具不同,就根据实质情况来选)

在 Format for output netlist 中,选择 verilog HDL。

在 Time Scale 中,选择时间单位,我这里选择的是 100ps。

其他默认即可。

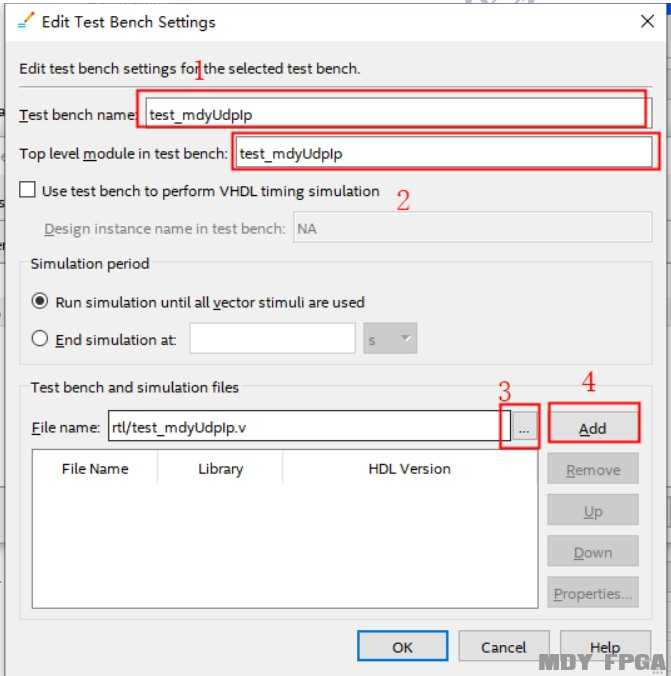

点击 Test Benches 按键,开始进行测试文件设置。

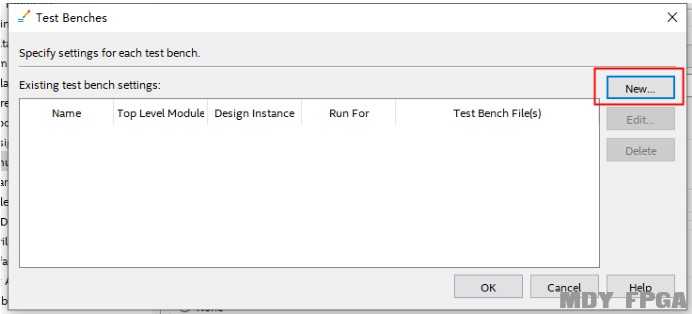

在弹出的窗口中,点击 New,开始新增一个测试文件。

在 Test bench name 中,填写测试文件名。本次演示工程中,测试文件名是test_mdyUdpIp。

在 Top level module in test bench 中,填写测试文件中的模块名,即 module name。一般

规范的是模块名与测试文件名一致,所以填 test_mdyUdpIp。

注意以上两个选项概念是不同的。有些人的模块名与文件名不一致,这个要注意下。

在上图 3 处,点击后选择测试文件,然后在 Add 中点击,即可添加测试文件。

当设置完成后,一路按 OK\APPLY 选项,关闭设置窗口。

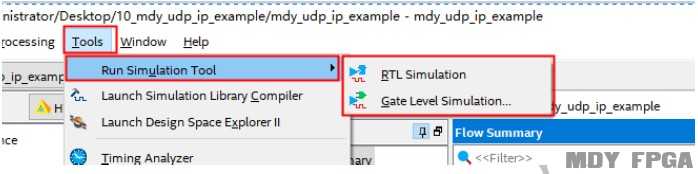

3. 运行 RTL 仿真

在 QUARTUS 界面中,在 tools 中,选择 Run Simulaton Tool,再选择 RTL Simulaton。

此时开始调用 MODELSIM 进行综合编译和仿真。

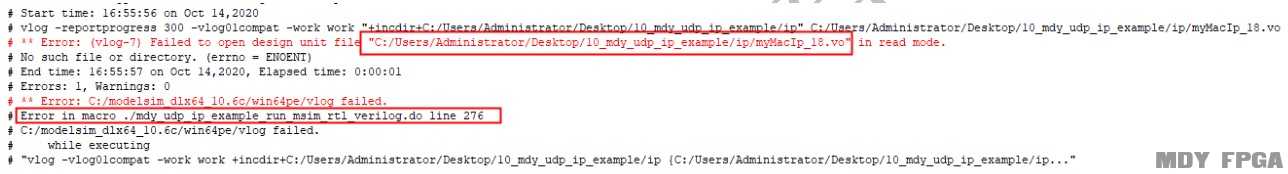

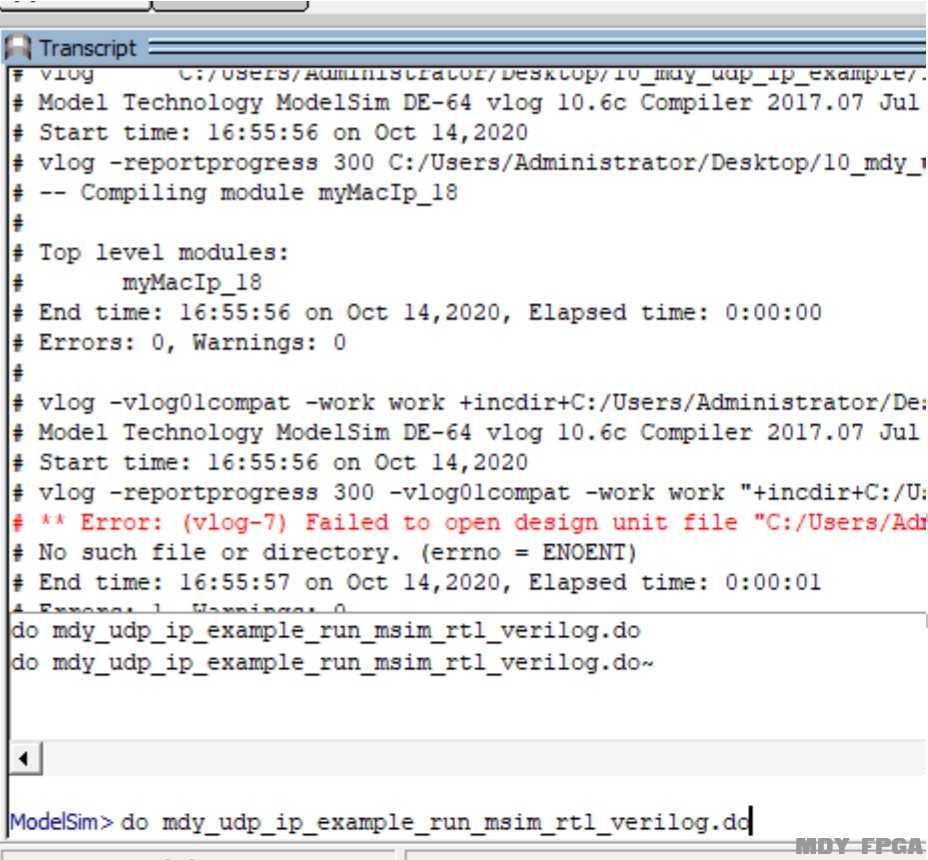

MODELSIM 有可能会出现上面的错误。

仔细阅读错误提示,该提示说找不到 myUdpIp_18.vo 文件。并且是在运行“udp_ip_example_run_msim_rtl_verilog.do”第 276 行时出现的错误。

笔者在目录下确实找不到 myUdpIp_18.vo 文件,百思不得其解,这个文件是哪里来的?!

不得已,去找 udp_ip_example_run_msim_rtl_verilog.do 看看。

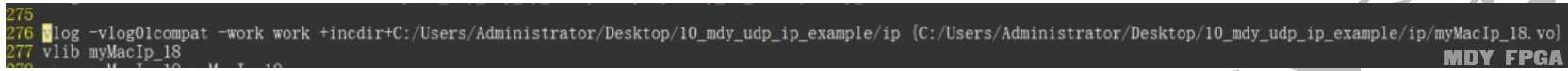

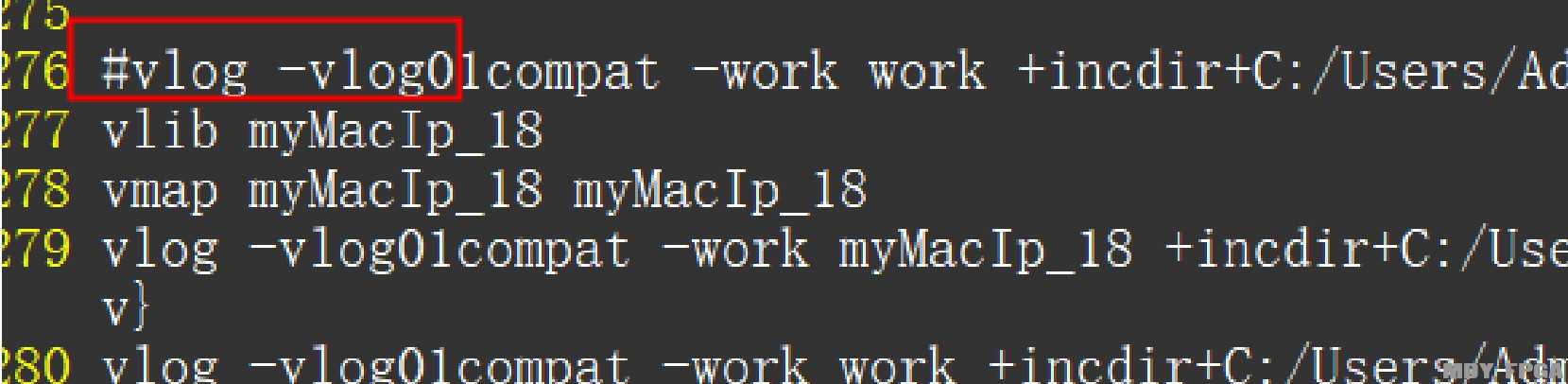

如上图,找到 udp_ip_example_run_msim_rtl_verilog.do 文件。

找到 276 行,确实是有一条语句要编译 myUdpIp_18.vo 文件。仍然不明白为什么要编

译:是生成的 IP 核少了这个文件,还是说测试时多要求了这个文件。

没有办法的情况下,将 276 行屏蔽,尝试不用此语句是否能成功。如上图所示,加一个#,保存。

修改后,注意注意!是在 MODELSIM 的窗口中,按“向上箭头”键,找到上面的语句do udp_ip_example_run_msim_rtl_verilog.do,按回车执行。

千万不要在 QUARTUS 里调用仿真,那样又会修改回 do 文件的。

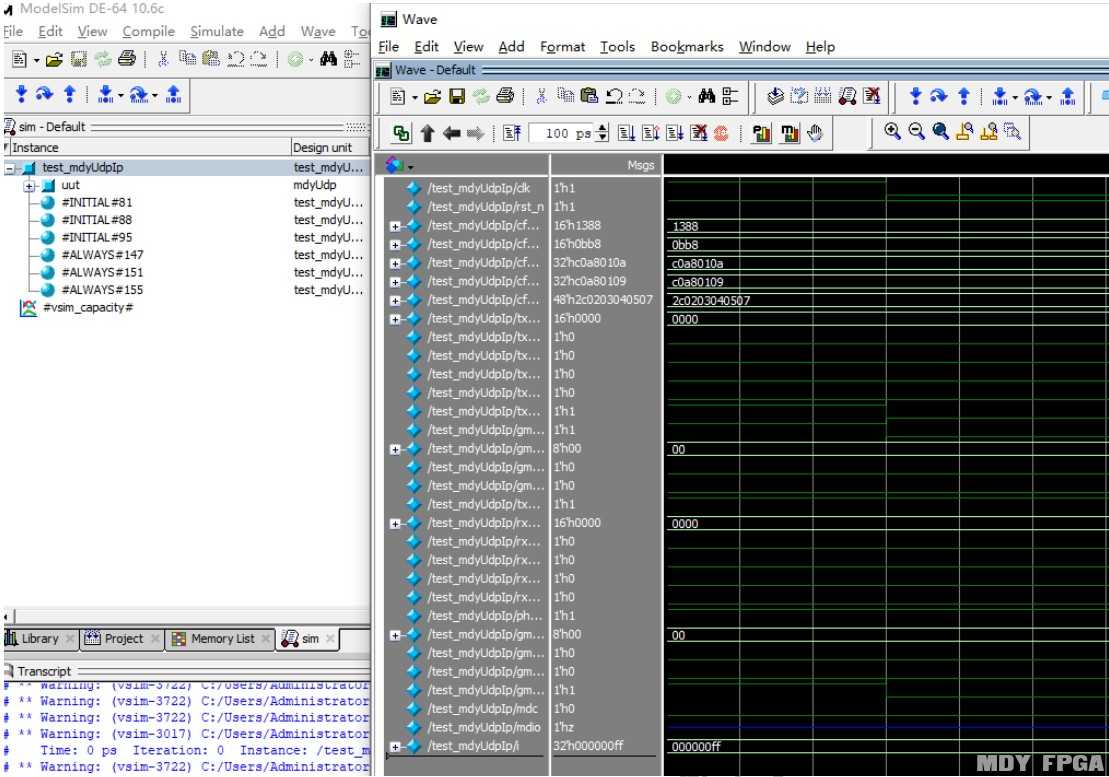

执行后果然没有问题,一切顺利,如上图所示。大家可以自由使用了。

4. 修改代码调试

当仿真发现问题,修改完代码后。没有必要从第 3 步开始(即不用 QUARTUS 调用MODELSIM)。而是直接在 MODELSIM 窗口中,选择 compile,选择修改的文件,compile。

然后在 MODELSIM 中 Restart,重新跑即可。