本文为明德扬原创文章,转载请注明出处!

本文以一个案例的形式来介绍lattice DDR3 IP核的生成及调用过程,同时介绍各个接口信号的功能作用:

一、建立Lattice工程

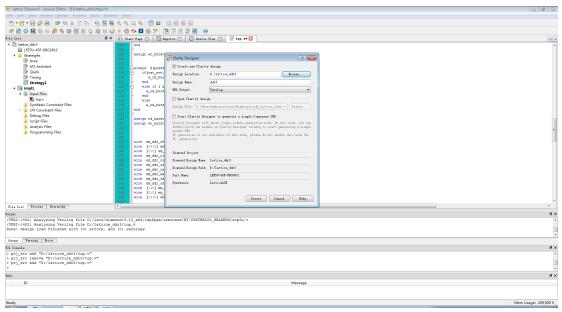

1、首先,新建一个工程“lattice_ddr3”:

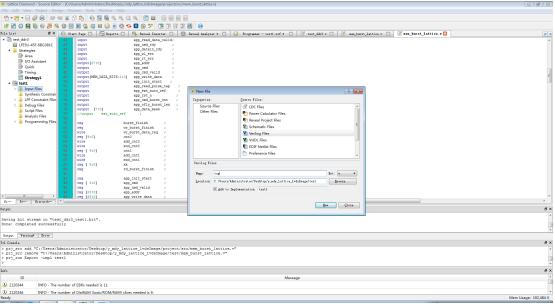

其中器件选择的是ECP5U系列LFE5U-45F-CABGA381芯片,Lattice的工程后缀是.ldf文件。进入工程界面后,添加模块文件:右键点击Input Files --Add--New File--Verilog Files即可添加。

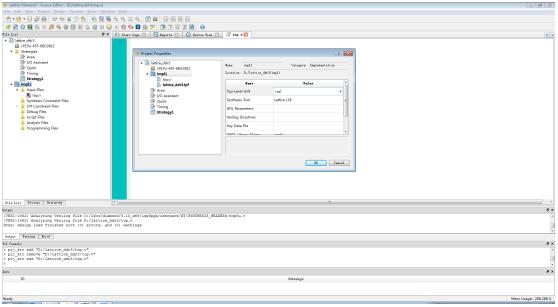

2、添加了工程文件后,需要设置一个顶层,右键点击impl1,选择Set Top-Level unit,在弹出的窗口中设置顶层文件的名称,综合软件选择系统自带的Lattice LSE。

二、顶层文件设计

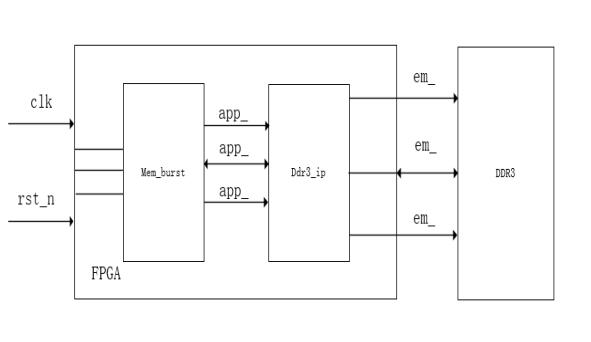

顶层文件中,需要包含输入输出信号,其中系统的输入是时钟clk和复位信号rst_n,输出是FPGA向DDR3的输出信号,信号的流程图如下所示:

其中,IP核控制模块Mem_burst中是双端口的输入输出,输入信号有顶层中产生的输入和IP核返回的输入信号;输出有IP核输出到Mem_burst的信号和控制模块输出到顶层的信号。

三、模块信号功能介绍:

DDR3 IP核的调用主要有两部分模块,分别是控制模块和IP核接口模块,其对应的各信号列表如下:

1、控制模块的信号功能列表如下所示:

|

信号名 |

位宽 |

I/O |

功能 |

|

clk |

1 |

I |

工作时钟,由IP核输出时钟sclk提供 |

|

rst_n |

1 |

I |

复位信号,低电平有效 |

|

rd_burst_req |

1 |

I |

外部输入读请求信号 |

|

wr_burst_req |

1 |

I |

外部输入写请求信号 |

|

rd_burst_addr |

28 |

I |

外部输入读请求地址 |

|

wr_burst_addr |

28 |

I |

外部输入写请求地址 |

|

rd_burst_data_valid |

1 |

O |

控制模块读出到外部的有效数据 |

|

wr_burst_data_req |

1 |

O |

控制模快输出到外部的写请求确认信号,外部收到此信号,开始写入数据 |

|

rd_burst_data |

64 |

O |

控制模块输出到外部的数据 |

|

wr_burst_data |

64 |

I |

外部输入的写数据 |

|

burst_finish |

1 |

O |

|

|

app_rst_n |

1 |

O |

控制器输出的IP核复位信号 |

|

app_init_start |

1 |

O |

控制器输出的IP核初始化开始信号 |

|

app_cmd |

4 |

O |

控制器输出的IP核指令信号 |

|

app_cmd_valid |

1 |

O |

控制器输出的IP核指令有效信号 |

|

app_addr |

28 |

O |

控制器输出的IP核地址信号 |

|

app_cmd_burst_cnt |

1 |

O |

命令突发计数输出,指示给定的读或写命令被控制器自动重复的次数。控制器还根据命令的突发长度顺序生成每个重复命令的地址 |

|

app_ofly_burst_len |

1 |

O |

控制器输出的当前命令及时突发长度 |

|

app_write_data |

64 |

O |

控制器输出给IP核的外部写入数据 |

|

app_data_mask |

8 |

O |

用于写数据的数据掩码。每个位屏蔽本地写数据的对应字节 |

|

app_init_done |

1 |

I |

IP核输入的初始化完成信号 |

|

app_cmd_rdy |

1 |

I |

IP核输入的命令准备信号 |

|

app_datain_rdy |

1 |

I |

IP核输入的数据写入准备信号 |

|

app_read_data |

64 |

I |

IP核输入的从DDR3中输出的数据 |

|

app_read_data_valid |

1 |

I |

IP核输入的读出数据有效信号 |

|

app_wl_err |

1 |

I |

IP核输入的写错误指示信号 |

|

app_rt_err |

1 |

I |

IP核输入的读错误指示信号 |

2、DDR3 IP核的接口信号功能列表如下:

|

信号名 |

位宽 |

I/O |

功能 |

|

clk_in |

1 |

I |

系统的工作时钟 |

|

rst_n |

1 |

I |

复位信号,低电平有效 |

|

app_rst_n |

1 |

I |

异步复位信号,只对内存设备进行复位,不会重置IP核 |

|

app_init_start |

1 |

I |

IP核初始化开始信号 |

|

app_cmd |

4 |

I |

IP核指令信号 |

|

app_cmd_valid |

1 |

I |

IP核指令有效信号 |

|

app_addr |

28 |

I |

控制器输出的IP核地址信号 |

|

app_cmd_burst_cnt |

1 |

I |

命令突发计数输出,指示给定的读或写命令被控制器自动重复的次数。控制器还根据命令的突发长度顺序生成每个重复命令的地址 |

|

app_ofly_burst_len |

1 |

I |

当前命令及时突发长度 |

|

app_write_data |

64 |

I |

控制器输出给IP核的外部写入数据 |

|

app_data_mask |

8 |

I |

用于写数据的数据掩码。每个位屏蔽本地写数据的对应字节 |

|

clocking_good |

1 |

O |

时钟稳定信号 |

|

burst_finish |

1 |

O |

突发读/写操作完成 |

|

app_init_done |

1 |

O |

IP核输出的初始化完成信号 |

|

app_cmd_rdy |

1 |

O |

命令准备输出信号,有效时表示内存准备好接收下一个命令和对应的地址,只持续一个时钟周期 |

|

app_datain_rdy |

1 |

O |

IP核输出的数据输入准备完成输出信号。当它有效时,表示内存已经准备好接收数据 |

|

app_read_data |

64 |

O |

IP核输入的从DDR3中输出的数据 |

|

app_read_data_valid |

1 |

O |

读数据有效输出信号,当其有效时,表示数据总线上的数据有效读出 |

|

app_wl_err |

1 |

O |

IP核输出的写错误指示信号 |

|

app_rt_err |

1 |

O |

IP核输出的读错误指示信号 |

|

em_ddr_addr |

15 |

O |

内存地址总线,内存的多路复用行和列地址。 |

|

em_ddr_ba |

3 |

O |

内存的bank地址 |

|

em_ddr_cke |

1 |

O |

控制器生成的内存时钟使能信号 |

|

em_ddr_clk |

1 |

O |

控制器产生的内存时钟,最高可达到400M |

|

em_ddr_cs_n |

1 |

O |

内存片选 |

|

em_ddr_data |

16 |

I/O |

内存双向数据总线 |

|

em_ddr_dm |

2 |

O |

DDR3内存写数据掩码,为字节级写屏蔽字节通道 |

|

em_ddr_dqs |

2 |

I/O |

内存双向数据频闪 |

|

em_ddr_odt |

1 |

O |

内存终止控制 |

|

em_ddr_cas_n |

1 |

O |

内存列地址频闪 |

|

em_ddr_ras_n |

1 |

O |

内存行地址频闪 |

|

em_ddr_reset_n |

1 |

O |

IP核向内存发送的异步复位信号,低电平有效 |

|

em_ddr_we_n |

1 |

O |

内存写使能 |

四、DDR3 IP核生成过程:

在例化DDR3的IP核之前,需要先生成DDR3的IP核,且DDR3的例化与其他IP核不同,具体的过程如下:

1、首先打开Clarity Designer创建一个IP文件:

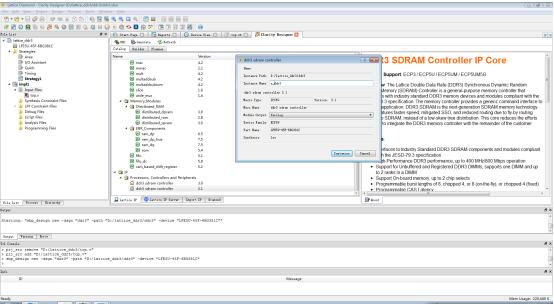

2、进入IP核生成界面后,需要在网上下载DDR3的IP核,在Lattice IP Sever中进行联网下载DDR3的IP核并安装,安装完IP核后在Lattice IP中选择ddr3 sdram controller 3.1,进行IP核参数设计:

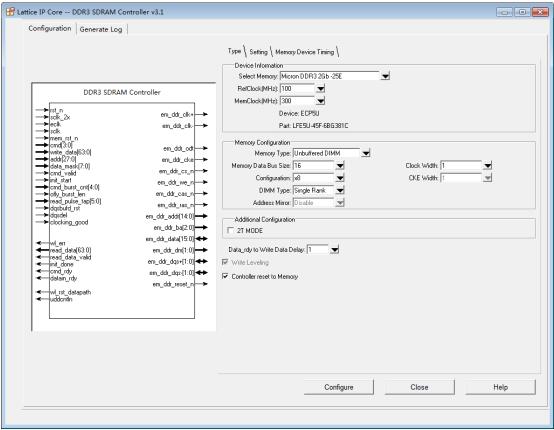

3、配置IP核参数,由于选取的器件是ECP5U系列FPGA,因此DDR3的频率需设置为300M,否则生成的IP核是灰色的无法加入工程中去,内存数据总线大小选择16,对应的输入数据位宽是64位,配置选择X8,对应的地址位宽是28位。

4、IP核生成完成后,点击系统IP核界面上Generate,会在工程的文件列表中加入一个.sbx文件,此文件就是需要例化的DDR3 IP核实体文件,同时在对应的文件夹下面会出现一个对应名称的.V文件,将这个.V文件中的信号例化进顶层中即可。

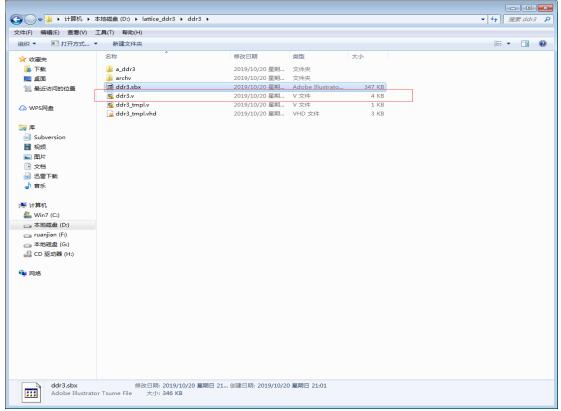

5、需要例化的.V文件:

五、例化IP核

将上图中的.V文件例化进顶层文件中,定义好信号类型,将对应的信号相连接。至此,DDR3的IP核添加成功。

以上就是lattice DDR3 IP核使用调试的内容分享,加QQ 3358622769 与我进行更深入的讨论!