《FPGA入门基础》 -- FFT IP核(Quartus)

前言:为了突出重点,仅对I/O数据流为steaming的情况作简要说明,以便快速上手,有关FFT ip核模型及每种设置详细介绍请参考官方手册FFT MegaCore Function User Guide。

1、 关于配置问题

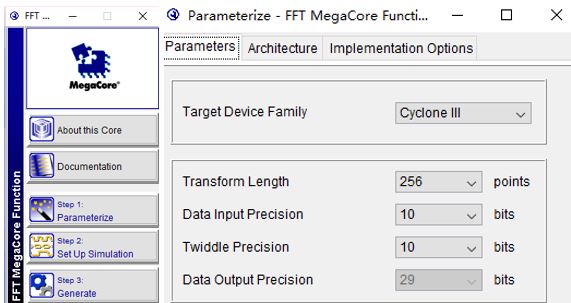

在FFT Megacore Function中选择“parameterize”,弹出对话框。

“Parameters”栏中,选择器件、转换数据的长度、数据精度已经旋转因子的精度。注意旋转因子精度必须小于等于数据精度。

“Architecture”栏中,有FFT引擎选择,在I/O数据流选择Streanming(流水线)的时候,引擎默认为1个四输出引擎。

img

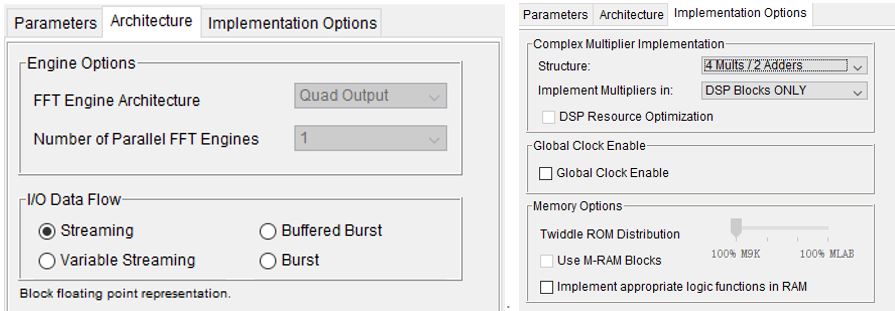

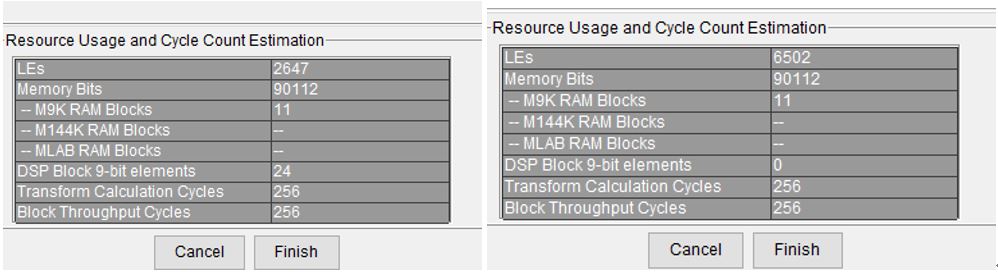

“Implementation Options”栏中,Structure中选择乘法器和加法器组合,有4 Mults/2 Adders和3 Mults/5 Adders两种,本例选择前者。Implement Multiplier in代表实现FFT的逻辑资源分配形式,有DSP Blocks/Logic cells、DSP Blocks ONLY和Logic Cells ONLY三种,Logic cells顾名思义就是消耗FPGA的逻辑资源,而DSP Blocks则将一部分逻辑资源用Embedded Multiplier 9-bit elements表示。本例选择DSP Blocks/Logic cells混合模式。全局时钟和存储器选择采用默认方式。

FFT Megacore Function中“step 2”为跟仿真有关的选项,根据需求选择即可。

“step 3”生成IP核。注意,在生成IP核的过程中,进度条可能会卡主不动,可能是破解的问题(版本13.1)。遇到该问题时,多试几次,或者改动设计参数,可能会顺利生成。

2、 信号说明

生成的FFT IP核,其端口列表如下,相关的详细说明可以在官方手册中查到:

端口说明:

| 端口 | 端口类型 | 说明 |

|---|---|---|

| Inverse | / | 改变FFT变换方向,置1时为FFI的你变换。 |

| Sink_valid | I | 拉高表示通知FFT即将有N个数据输入 |

| Sink_sop | I | 输入数据起始标记脉冲(维持一个时钟的高电平),与第一个数据同步 |

| Sink_eop | I | 输入数据结束标记脉冲(维持一个时钟的高电平),与最后一个数据同步 |

| Sink_real | I | 输入数据的实部 |

| Sink_imag | I | 输入数据的虚部 |

| sink_error | I | 指示数据流的错误信息:00——没有错误;01——丢失SOP;10——丢失EOP;11——多余的EOP; |

| sink_ready | O | FFT模块准备就绪,可以接收数据 |

| source_ready | I | 表明downstream模块(理解为FFT的后续接收数据模块)可以接收数据 |

| source_error | O | 表明upstream模块或者FFT模块出了问题,错误信息提示与sink_error一样 |

| source_sop | O | 输出数据起始标记 |

| source_eop | O | 输出数据结束标记 |

| source_valid | O | 置高,准备输出结果 |

| source_exp | O | 结果数据缩放因子:这个指数位的意思打个比方说吧,比如它是3,就是说这时输出的虚部和实部的数值要除以2的3次方,如果是10,就要除以2的10次方,如果对结果精度要求不高的话,可以直接截去相应的长度,比如指数是3,实部输出101101110111,那么此刻实际的值应该为101101110.111;取整就是101101110 |

| source_real | O | 变换后输出数据的实部 |

| source_imag | O | 变换后输出数据的虚部 |

3 、FPGA仿真结果

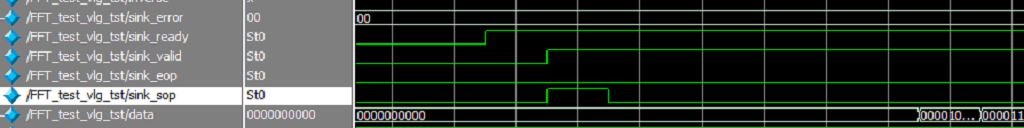

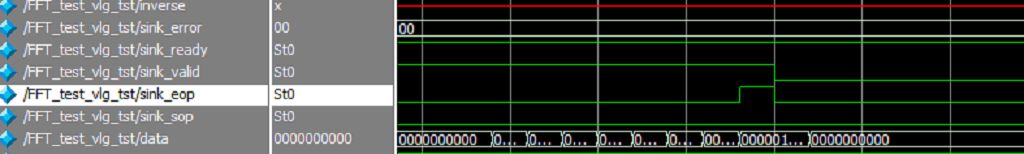

sink_ready由FFT模块发出,代表其准备就绪。复位至少数个周期。当复位失效,FFT准备就绪后,sink_ready被置高。将Sink_valid拉高,通知FFT准备接收发来的数据。Sink_sop代表流水线输入数据的开始,在Sink_sop拉高的同时,第一个数据已经发送。

当一帧的数据(FFT处理的点数)输出完成后,将sink_eop拉高,代表一帧数据的结束,注意最后一个数据在sink_eop拉高的同时传输。注意:如果多帧数据连续输入,为了简化程序设计,将两帧数据中间放置一个时钟的周期的间隔,此时必须将Sink_valid拉低一个时钟周期,否则FFT的sourse_error会报01的错误,即缺少数据开始标志Sink_sop。当然,在程序设计上让Sink_sop和sink_eop首尾相连,则不需要拉低一个周期的Sink_valid。

在数个时钟周期之后,FFT模块开始输出转换完成的数据。与输入相似,当完成时,FFT模块会拉高转换完成信号source_valid和输出起始标志信号source_sop,与此同时,第一个数据输出。

当一帧数据转换完成后,FFT模块会将source_eop拉高,同时输出最后一个转换完成的数据。