明德杨FPGA入门篇——Verilog计数器

本文为明德扬原创文章,转载请注明出处! 作者:卢靖东

一、Verilog介绍

Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。Verilog HDL和VHDL是世界上最流行的两种硬件描述语言,都是在20世纪80年代中期开发出来的。前者由Gateway Design Automation公司(该公司于1989年被Cadence公司收购)开发。两种HDL均为IEEE标准。

二、Verilog计数器实测

例题:

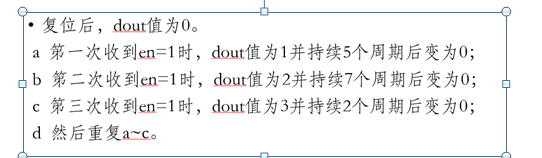

我们用 明德杨《至简设计法》--八部计数法来分析此题

1.明确目标:找输入输出并绘画I/O表

① 输入输出:

1.模块时钟,D触发器中clk和rst_n为输入,位宽默认为1。

2.题目给出输出为dout,位宽和时钟默认为1。

② I/O表:

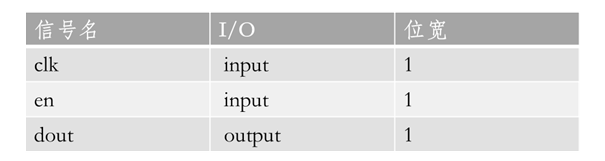

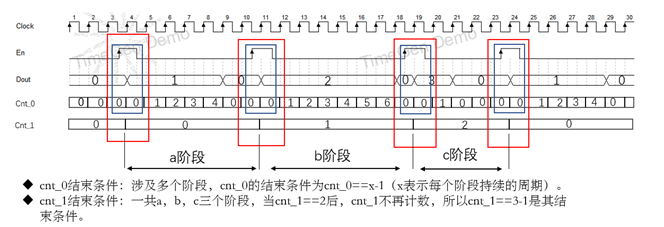

2.画波形图

① 根据题目分析绘画波形图

先看第一个阶段a部分:

|

1.复位后,dout值为0,dout初始值为0。 |

|

2.收到信号en=1时,dout由0 → 1并持续五个周期后,由 |

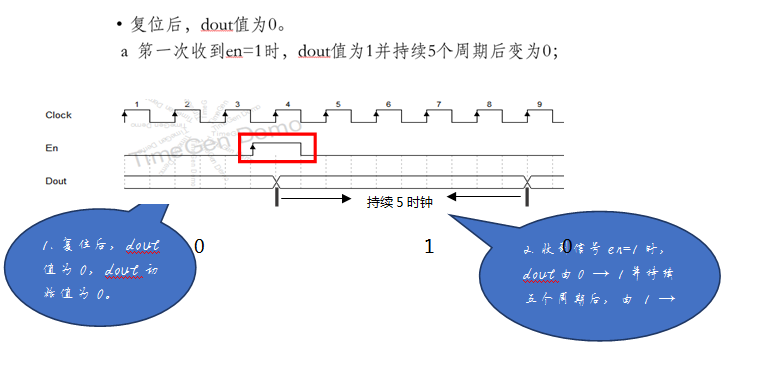

完成第一阶段后继续后面的内容:

3.计数框架

① 计数结构:

以该题为例,题目要求多次收到en的信号,多个阶段的信号处理,所以

我们可以优先考虑使用两个计数器,命名为cnt_0和cnt_1,分别来记录en=1

后dout处于哪个阶段。

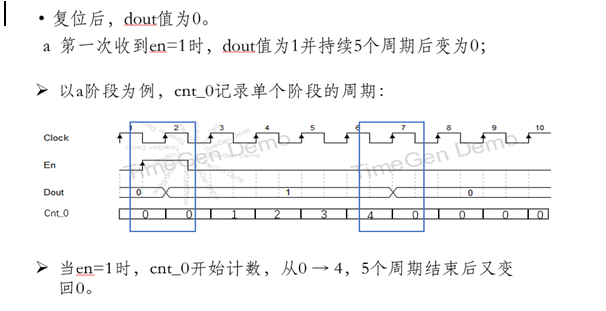

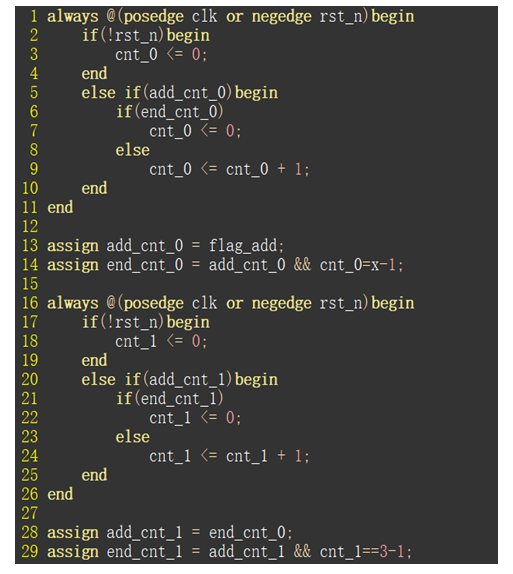

4.加一结束条件

u cnt_0加1条件:收到en的信号后,利用变量flag_add辅助来持续周期,所以cnt_0=flag_add为

加1条件。

u cnt_1加1条件:当cnt_0完成一个阶段计数后,每收到en的信号,cnt_1就开始计数,完成一个阶段cnt_1加1,所以 cnt_1=end_cnt_0 为加1条件。

5.定义特殊点

① 将需要的特殊点挑选出来,并用信号表示

SHAPE \* MERGEFORMAT

|

a 整个功能的开始点:en; b cnt_0的结束条件:cnt _0= x-1,定为end_cnt_0; c cnt_1的结束条件:cnt_1= 3-1,定为end_cnt_1; d dout变高条件:en==1。 |

6.完整性检查

保证每个信号的变化条件已经清晰明确,并且变化条件要用信号表示。

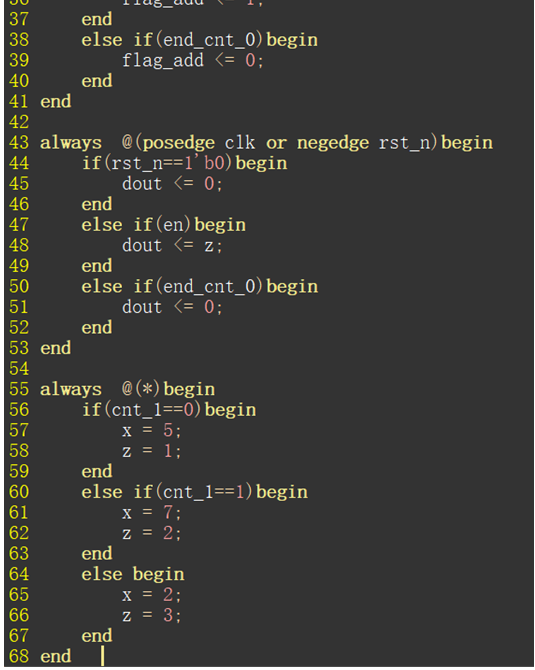

SHAPE \* MERGEFORMAT

z是数值

7.计数器代码

Ø 计数器框架、加1条件和结束条件代码

8.功能代码

Ø 按照完整性检查,写出计数器之外的代码。

最后仿真检测一下代码:

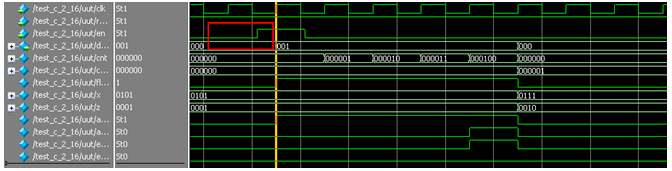

第一次接收到en信号

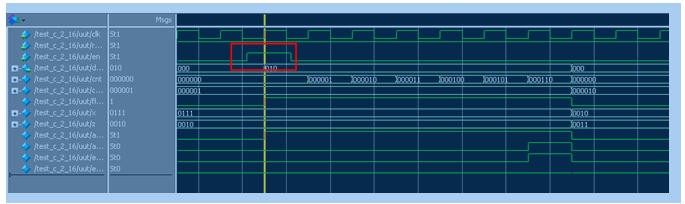

第二次接收到en信号

第三次接收到en的信号

以上就是Verilog计数器部分的内容分享,更多FPGA使用技巧加Q:2332395003交流学习!