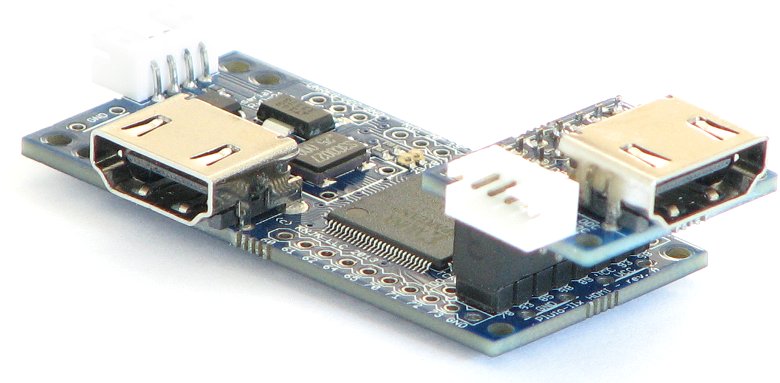

连接器

-

TMD时钟+和时钟- -

TMDs data 0+和data 0- -

TMDs data 1+和data 1- -

TMDs data 2+和data 2-

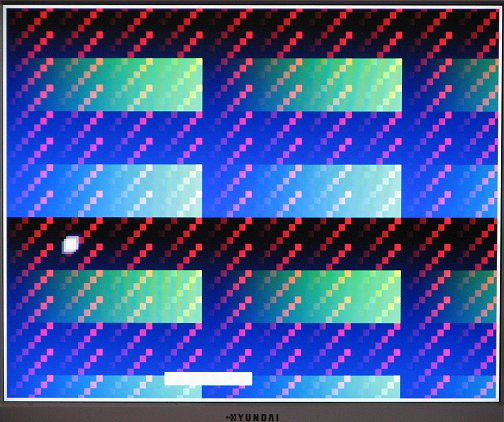

视频信号

TMD信号

源代码

reg [9:0] CounterX; // counts from 0 to 799 always @(posedge pixclk) CounterX <= (CounterX==799) ? 0 : CounterX+1; reg [9:0] CounterY; // counts from 0 to 524 always @(posedge pixclk) if(CounterX==799) CounterY <= (CounterY==524) ? 0 : CounterY+1;

wire hSync = (CounterX>=656) && (CounterX<752); wire vSync = (CounterY>=490) && (CounterY<492); wire DrawArea = (CounterX<640) && (CounterY<480);

wire [7:0] red = {CounterX[5:0] & {6{CounterY[4:3]==~CounterX[4:3]}}, 2'b00}; wire [7:0] green = CounterX[7:0] & {8{CounterY[6]}}; wire [7:0] blue = CounterY[7:0];

wire [9:0] TMDS_red, TMDS_green, TMDS_blue;

TMDS_encoder encode_R(.clk(pixclk), .VD(red ), .TMDS(TMDS_red) , .CD(2'b00) , .VDE(DrawArea));

TMDS_encoder encode_G(.clk(pixclk), .VD(green), .TMDS(TMDS_green), .CD(2'b00) , .VDE(DrawArea));

TMDS_encoder encode_B(.clk(pixclk), .VD(blue ), .TMDS(TMDS_blue) , .CD({vSync,hSync}), .VDE(DrawArea));

wire clk_TMDS, DCM_TMDS_CLKFX; DCM_SP #(.CLKFX_MULTIPLY(10)) DCM_TMDS_inst(.CLKIN(pixclk), .CLKFX(DCM_TMDS_CLKFX), .RST(1'b0)); BUFG BUFG_TMDSp(.I(DCM_TMDS_CLKFX), .O(clk_TMDS)); // 250 MHz

reg [3:0] TMDS_mod10; // modulus 10 counter always @(posedge clk_TMDS) TMDS_mod10 <= (TMDS_mod10==9) ? 0 : TMDS_mod10+1; reg TMDS_shift_load; always @(posedge clk_TMDS) TMDS_shift_load <= (TMDS_mod10==9); reg [9:0] TMDS_shift_red, TMDS_shift_green, TMDS_shift_blue; always @(posedge clk_TMDS) begin TMDS_shift_red <= TMDS_shift_load ? TMDS_red : TMDS_shift_red [9:1];

TMDS_shift_green <= TMDS_shift_load ? TMDS_green : TMDS_shift_green[9:1];

TMDS_shift_blue <= TMDS_shift_load ? TMDS_blue : TMDS_shift_blue [9:1]; end

OBUFDS OBUFDS_red (.I(TMDS_shift_red [0]), .O(TMDSp[2]), .OB(TMDSn[2])); OBUFDS OBUFDS_green(.I(TMDS_shift_green[0]), .O(TMDSp[1]), .OB(TMDSn[1])); OBUFDS OBUFDS_blue (.I(TMDS_shift_blue [0]), .O(TMDSp[0]), .OB(TMDSn[0])); OBUFDS OBUFDS_clock(.I(pixclk), .O(TMDSp_clock), .OB(TMDSn_clock));

较高分辨率

截图