创始人兼 CEO

Auviz Systems

Nagesh@auvizsystems.com

凭借出色的性能和功耗指标,赛灵思 FPGA 成为设计人员构建卷积神经网络的首选 XE "" XE "" XE "" XE ""。新的软件工具可简化实现工作。

人工智能正在经历一场变革,这要得益于机器学习的快速进步。在机器学习领域,人们正对一类名为“深度学习”算法产生浓厚的兴趣,因为这类算法具有出色的大数据集性能。在深度学习中,机器可以在监督或不受监督的方式下从大量数据中学习一项任务。大规模监督式学习已经在图像识别和语音识别等任务中取得巨大成功。

深度学习技术使用大量已知数据找到一组权重和偏差值,以匹配预期结果。这个过程被称为训练,并会产生大型模式。这激励工程师倾向于利用专用硬件(例如 GPU)进行训练和分类。

随着数据量的进一步增加,机器学习将转移到云。大型机器学习模式实现在云端的 CPU 上。尽管 GPU 对深度学习算法而言在性能方面是一种更好的选择,但功耗要求之高使其只能用于高性能计算集群。因此,亟需一种能够加速算法又不会显著增加功耗的处理平台。在这样的背景下,FPGA 似乎是一种理想的选择,其固有特性有助于在低功耗条件下轻松启动众多并行过程。

让我们来详细了解一下如何在赛灵思 FPGA 上实现卷积神经网络 (CNN)。CNN 是一类深度神经网络,在处理大规模图像识别任务以及与机器学习类似的其他问题方面已大获成功。在当前案例中,针对在 FPGA 上实现 CNN 做一个可行性研究,看一下 FPGA 是否适用于解决大规模机器学习问题。

卷积神经网络是一种深度神经网络 (DNN),工程师最近开始将该技术用于各种识别任务。图像识别、语音识别和自然语言处理是 CNN 比较常见的几大应用。

什么是卷积神经网络?

卷积神经网络是一种深度神经网络 (DNN),工程师最近开始将该技术用于各种识别任务。图像识别、语音识别和自然语言处理是 CNN 比较常见的几大应用。

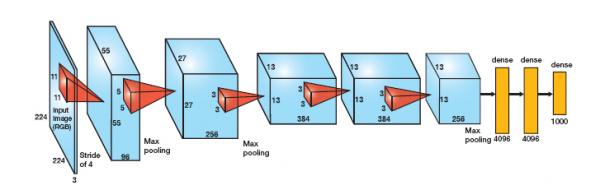

2012 年,Alex Krishevsky 与来自多伦多大学 (University of Toronto) 的其他研究人员 [1] 提出了一种基于 CNN 的深度架构,赢得了当年的“Imagenet 大规模视觉识别挑战”奖。他们的模型与竞争对手以及之前几年的模型相比在识别性能方面取得了实质性的提升。自此,AlexNet 成为了所有图像识别任务中的对比基准。

AlexNet 有五个卷积层和三个致密层(图 1)。每个卷积层将一组输入特征图与一组权值滤波器进行卷积,得到一组输出特征图。致密层是完全相连的一层,其中的每个输出均为所有输入的函数。

卷积层

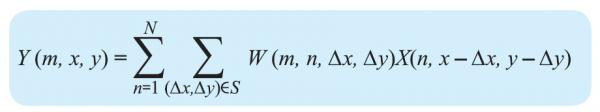

AlexNet 中的卷积层负责三大任务,如图 2 所示:3D 卷积;使用校正线性单元 (ReLu) 实现激活函数;子采样(最大池化)。3D 卷积可用以下公式表示:

其中Y(m,x,y)是输出特征图m位置(x,y)处的卷积输出,S是(x,y)周围的局部邻域,W是卷积滤波器组,X(n,x,y)是从输入特征图n上的像素位置(x,y)获得的卷积运算的输入。

图 1 – AlexNet 是一种图像识别基准,包含五个卷积层(蓝框)和三个致密层(黄)。

图 2 – AlexNet 中的卷积层执行 3D 卷积、激活和子采样。

所用的激活函数是一个校正线性单元,可执行函数Max(x,0)。激活函数会在网络的传递函数中引入非线性。最大池化是 AlexNet 中使用的子采样技术。使用该技术,只需选择像素局部邻域最大值传播到下一层。

定义致密层

AlexNet 中的致密层相当于完全连接的层,其中每个输入节点与每个输出节点相连。AlexNet 中的第一个致密层有 9,216 个输入节点。将这个向量乘以权值矩阵,以在 4,096 个输出节点中产生输出。在下一个致密层中,将这个 4,096 节点向量与另一个权值矩阵相乘得到 4,096 个输出。最后,使用 4,096 个输出通过 softmax regression 为 1,000 个类创建概率。

在 FPGA 上实现 CNN

随着新型高级设计环境的推出,软件开发人员可以更方便地将其设计移植到赛灵思 FPGA 中。软件开发人员可通过从 C/C++ 代码调用函数来充分利用 FPGA 与生俱来的架构优势。Auviz Systems 的库(例如 AuvizDNN)可为用户提供最佳函数,以便其针对各种应用创建定制 CNN。可在赛灵思 SD-Accel™ 这样的设计环境中调用这些函数,以在 FPGA 上启动内核。

最简单的方法是以顺序方式实现卷积和向量矩阵运算。考虑到所涉及计算量,因此顺序计算会产生较大时延。

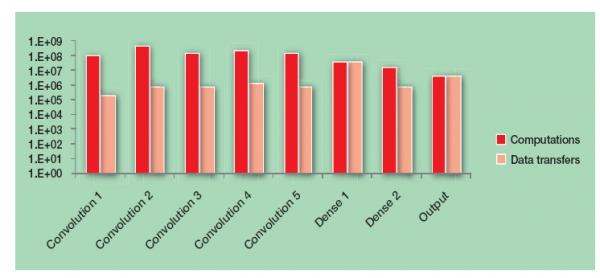

顺序实现产生很大时迟的主要原因在于 CNN 所涉及的计算的绝对数量。图 3 显示了 AlexNet 中每层的计算量和数据传输情况,以说明其复杂性。

图 3 – 图表展示了 AlexNet 中涉及的计算复杂性和数据传输数量。

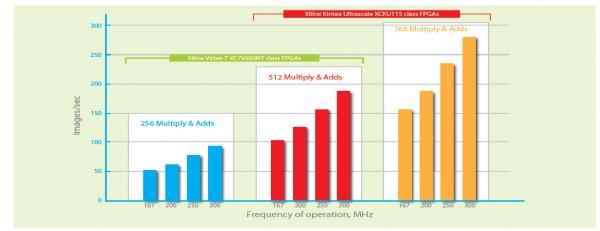

因此,很有必要采用并行计算。有很多方法可将实现过程并行化。图 6 给出了其中一种。在这里,将 11x11 的权值矩阵与一个 11x11 的输入特征图并行求卷积,以产生一个输出值。这个过程涉及 121 个并行的乘法-累加运算。根据 FPGA 的可用资源,我们可以并行对 512 抑或 768 个值求卷积。

为了进一步提升吞吐量,我们可以将实现过程进行流水线化。流水线能为需要一个周期以上才能完成的运算实现更高的吞吐量,例如浮点数乘法和加法。通过流水线处理,第一个输出的时延略有增加,但每个周期我们都可获得一个输出。

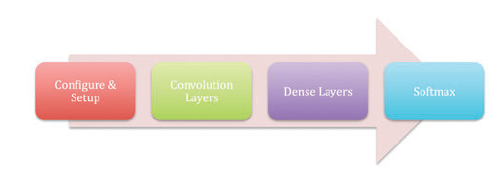

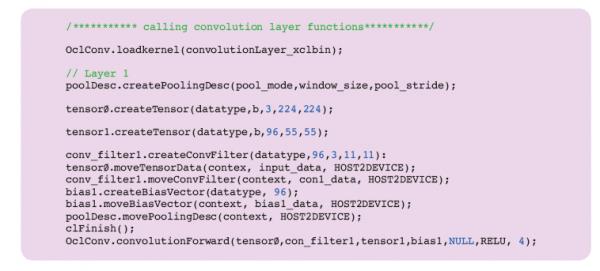

使用 AuvizDNN 在 FPGA 上实现的完整 CNN 就像从 C/C++ 程序中调用一连串函数。在建立对象和数据容器后,首先通过函数调用来创建每个卷积层,然后创建致密层,最后是创建 softmax 层,如图 4 所示。

图 4 - 实现 CNN 时的函数调用顺序。

图 5 – 使用 AuvizDNN 创建 AlexNet 的 L1 的代码片段。

图 6 – AlexNets 的性能因 FPGA 类型不同而不同。

AuvizDNN 是 Auviz Systems 公司提供的一种函数库,用于在 FPGA 上实现 CNN。该函数库提供轻松实现 CNN 所需的所有对象、类和函数。用户只需要提供所需的参数来创建不同的层。例如,图 5 中的代码片段显示了如何创建 AlexNet 中的第一层。

AuvizDNN 提供配置函数,用以创建 CNN 的任何类型和配置参数。AlexNet 仅用于演示说明。CNN 实现内容作为完整比特流载入 FPGA 并从 C/C++ 程序中调用,这使开发人员无需运行实现软件即可使用 AuvizDNN。

FPGA 具有大量的查找表 (LUT)、DSP 模块和片上存储器,因此是实现深度 CNN 的最佳选择。在数据中心,单位功耗性能比原始性能更为重要。数据中心需要高性能,但功耗要在数据中心服务器要求限值之内。

像赛灵思 Kintex® UltraScale™ 这样的 FPGA 器件可提供高于 14 张图像/秒/瓦特的性能,使其成为数据中心应用的理想选择。图 6 介绍了使用不同类型的 FPGA 所能实现的性能。

一切始于 c/c++

卷积神经网络备受青睐,并大规模部署用于处理图像识别、自然语言处理等众多任务。随着 CNN 从高性能计算应用 (HPC) 向数据中心迁移,需要采用高效方法来实现它们。

FPGA 可高效实现 CNN。FPGA 的具有出色的单位功耗性能,因此非常适用于数据中心。

AuvizDNN 函数库可用来在 FPGA 上实现 CNN。AuvizDNN 能降低 FPGA 的使用复杂性,并提供用户可从其 C/C++ 程序中调用的简单函数,用以在 FPGA 上实现加速。使用 AuvizDNN 时,可在 AuvizDNN 库中调用函数,因此实现 FPGA 加速与编写 C/C++ 程序没有太大区别。